Hi

We have questions for connection of HPD-SNK.

1.

I see there exists internal pull down resister at HPD_SNK.

However, its value seems to be different between Function Block Diagram and Figure 12.

(130Kohm on the Function Block Diagram, 190Kohm on the Figure 12).

Which is correct?

2.

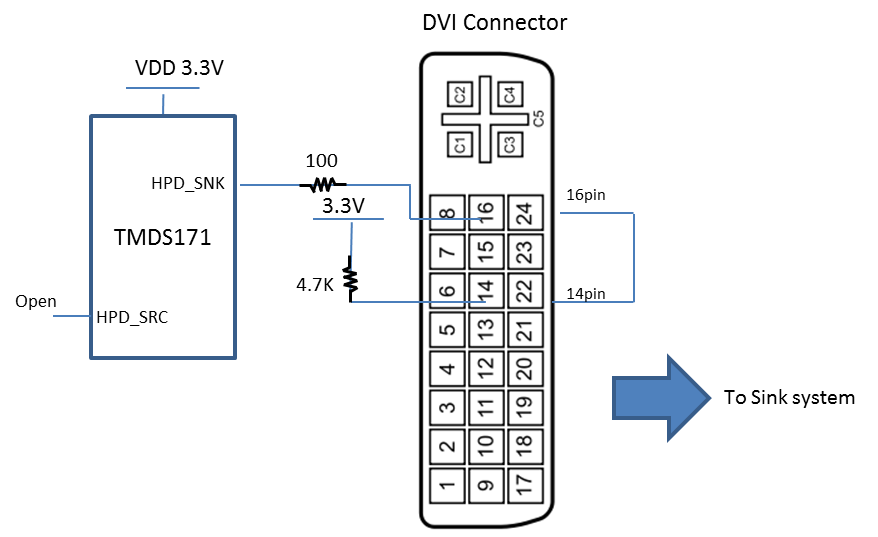

We are assuming the following connection.

Normally, I think 14pin supplies 5V to sink system as for pin placement of DVI connecor.

However, 5V from the DVI connector does not supply to the sink system in our configuration.

(The sink system has the 5V for HPD terminal by itself)

And the voltage applied to HPD_SNK of TMDS171 can be calculated as

3.3V * (Internal PD) / (Internal PD + 0.1 + 4.7) = 3.18V (If Internal pull down resistor was 130Kohm)

It would satisfy HPD VIH(min) = 2.1V > 3.18V, so I think it's OK.

Do you see any problem in our connection for HPD_SNK?

BestRegards