Dear Team,

our customer is facing a problem with the HDMI Input / TMDS181 on their prototype:

Sometimes it happens (after a video format change) that the TMDS channels are not correctly deskewed, and that the Deskewing even is different during the first active video line, compared to the other active video lines.

Please find below some scope images showing this malfunction on a video format : 1280 x 720 p @ 60Hz. (which was decoded as 1280 x 718 p @ 60 Hz by the TMDS decoder).

Please find more information below from the customer (high resolution of the graphs share via TI box).

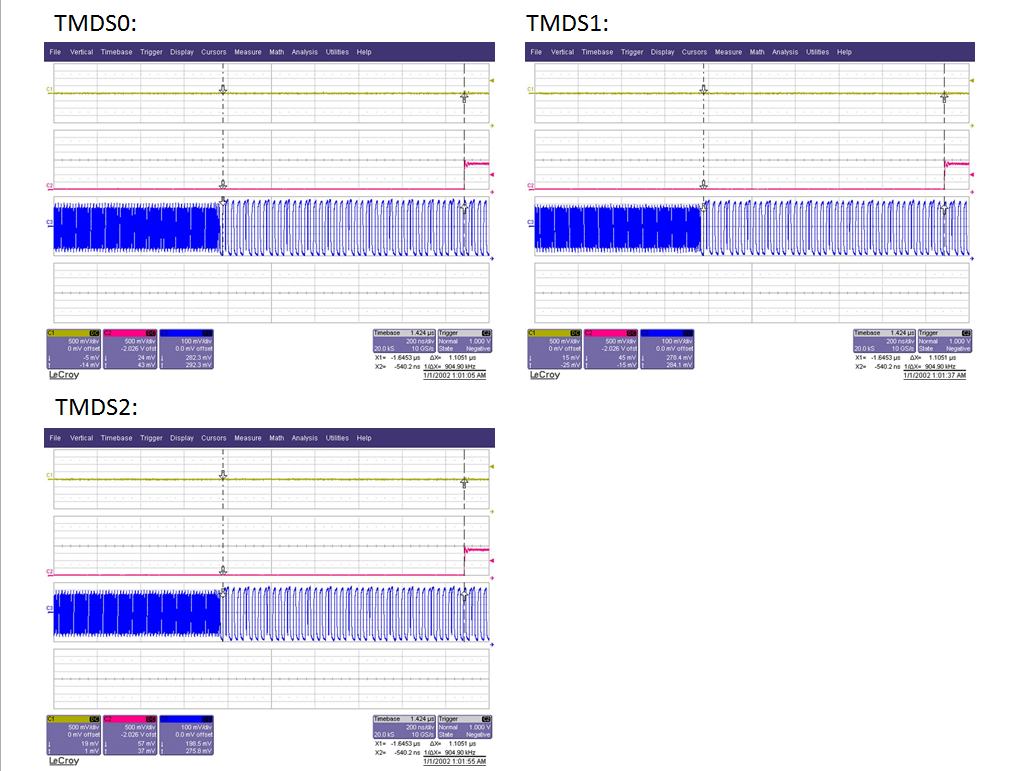

1) HDMI Input:

The skew for the first line on the input of the TMDS181 looks like this (C1 = Vertical Sync, C2 = Horizontal Sync, C3 = TMDS data (measured with differential probe)).

As you can see there is as good as no skew between the 3 different clock lines (the delay of 1.1051 us is referenced to the rising edge of the Horizontal sync that was decoded by our TMDS decoder).

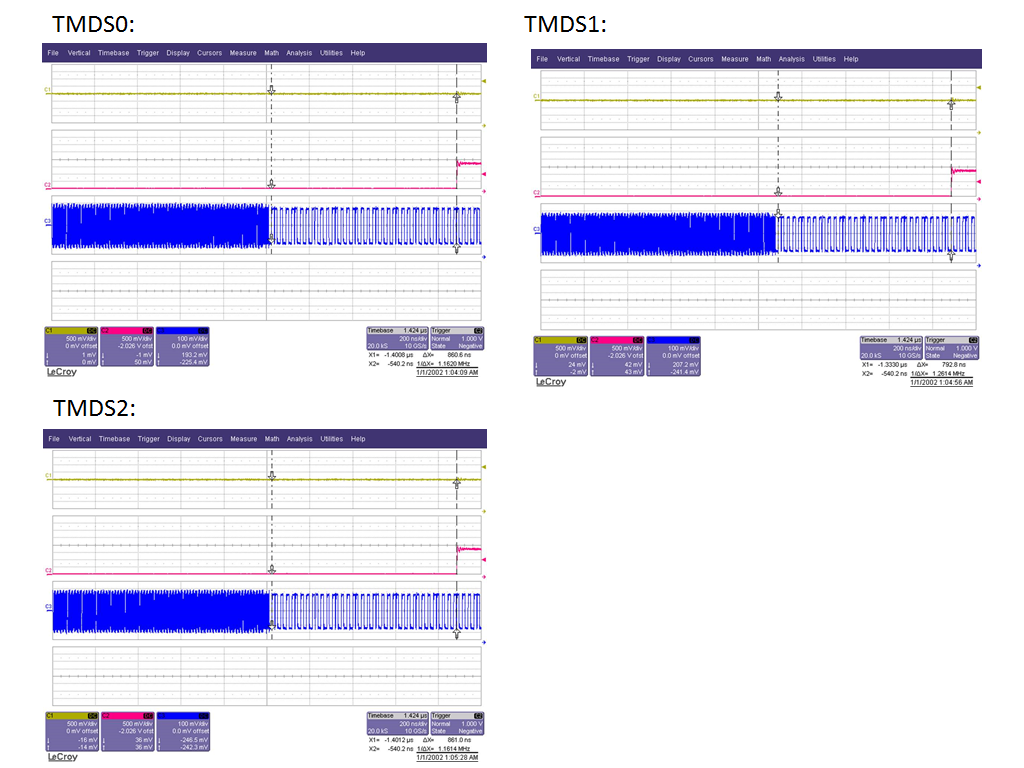

2) HDMI Output

When we take a look at the same signals at the output of the TMDS 181 for the first active line we can see this.

As you can see, there is as good as no skew between TMDS0 & TMDS2, but there is large skew between TMDS1 and the other channels of about 69ns (at a TMDS clock of 13ns this is about 5 TMDS clock cycles).

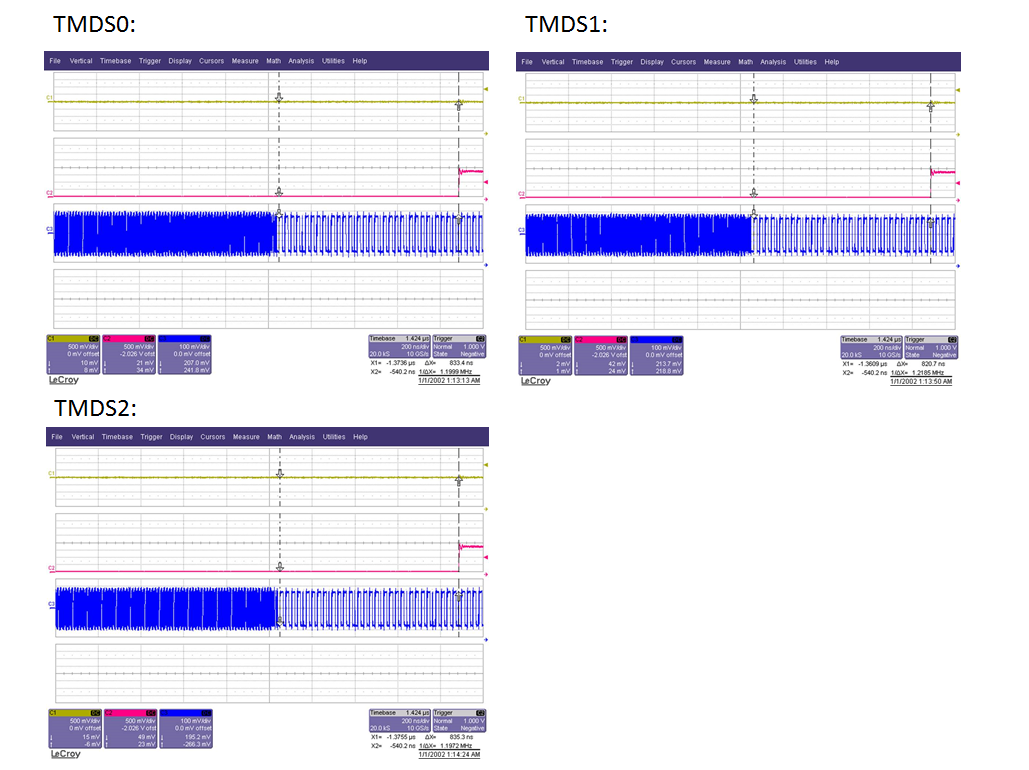

3) 2nd Video Line

When measuring the second active video line, we can see that the skew has changed.

Now there is almost no skew between the three channels. So the skew seems to have been changed between the first and the second active line.

This behaviour is confusing our TMDS decoder, making it to lose the first 2 active video lines.

Is this behaviour something that is known by TI engineering? What could cause it, can it somehow be prevented?

Be aware that we are using the TMDS181 in reclocking mode over the full range. I’m not sure if this has something to do with it?

When this happens (this only happens intermittently) it can be cured by rewriting the apply_RXTX_changes register in the TMDS181. Then all outputs are aligned perfectly.

Our problem is that if it is going wrong, we can not easily detect this, making it unclear when we would need to rewrite this bit and when not. Is there a way to read out the amount of skew at the output of the TMDS181 using the register interface?

Thanks and best regards

Martin