Hi Sirs,

Sorry to bother you.

As title, we have use SN65DSI84 and download tooling " sllc434c.zip "

We have some questions need check

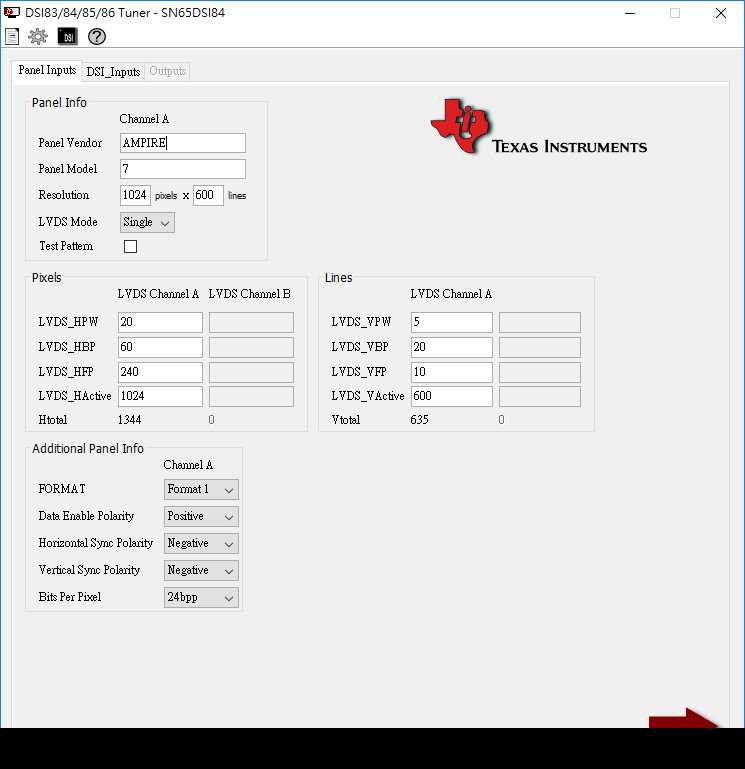

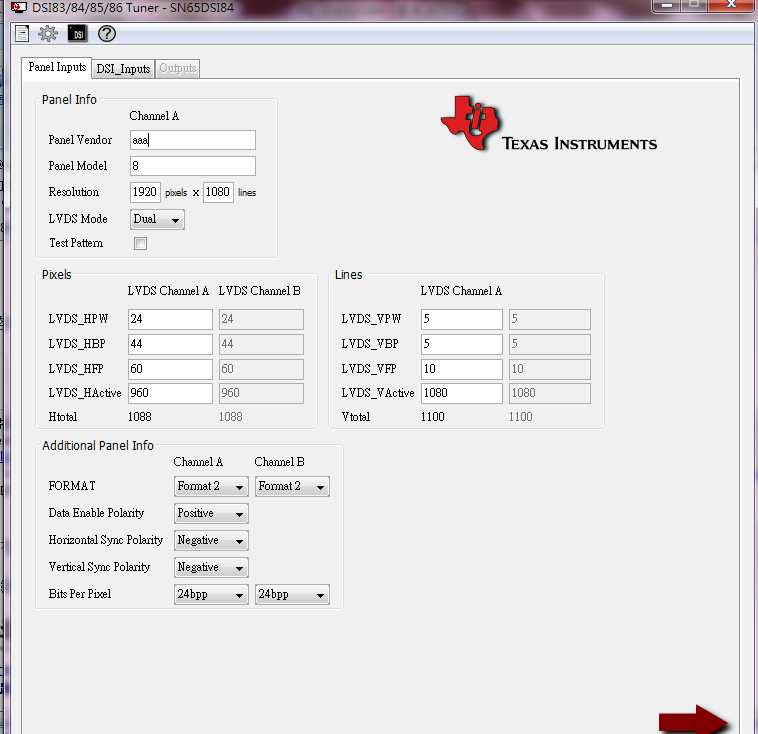

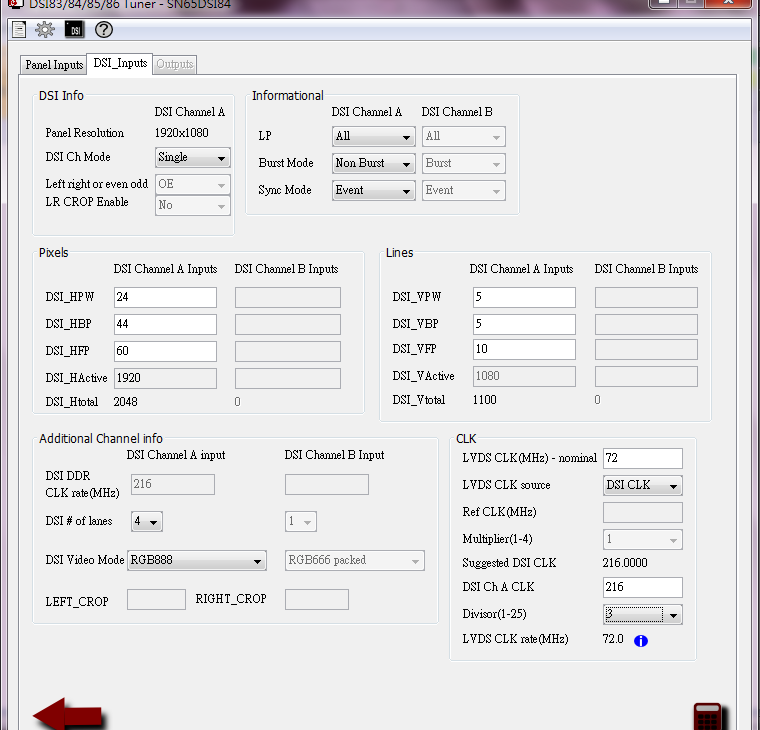

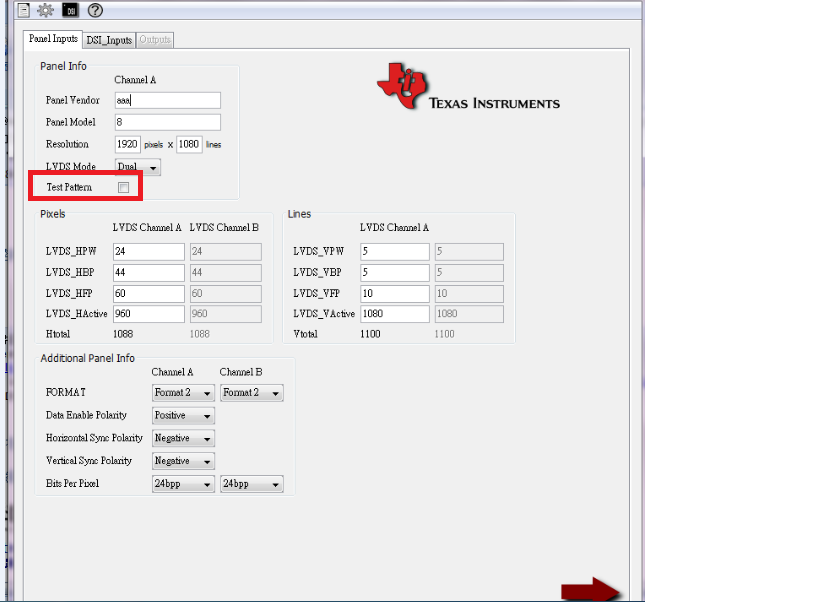

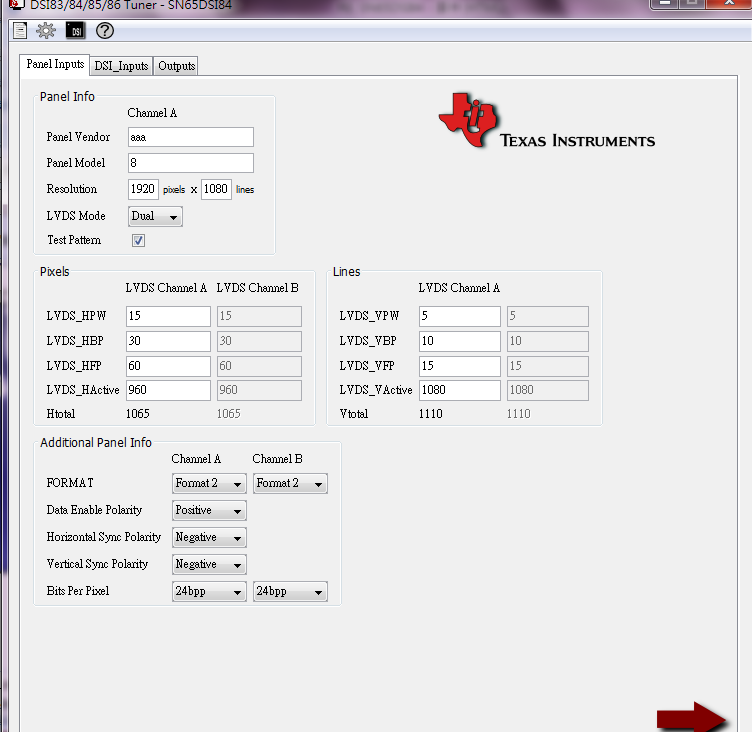

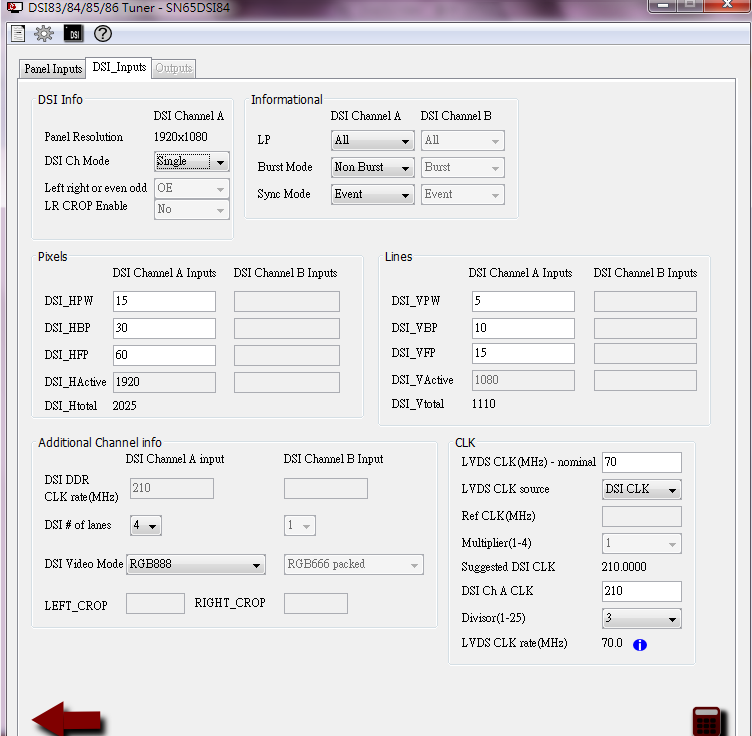

Our setting as below

We will transfer register data to be our initial code.

There have signal output from MIPI side, also CLK is normally.

But only Y2/CLK had output at DSI84 side, Y0/Y1/Y3 didn't.

The CLK result is same as our setting.

1. We would like to know why no output on Y0/Y1/Y3?

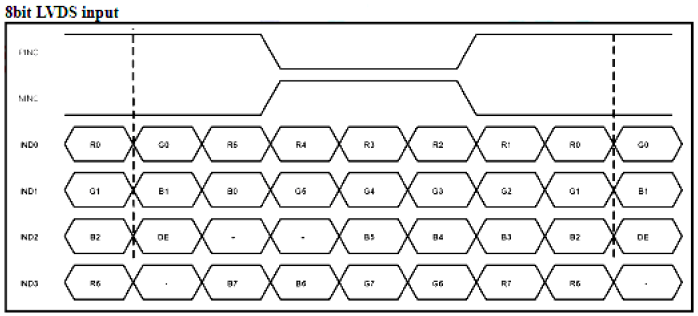

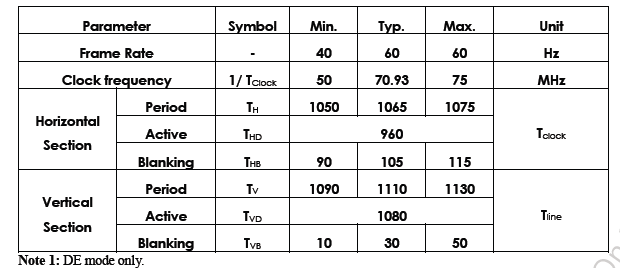

2. Does DSI84 could support LVDS format as below?

If Yes, how to setting? if no, have other solution can share?

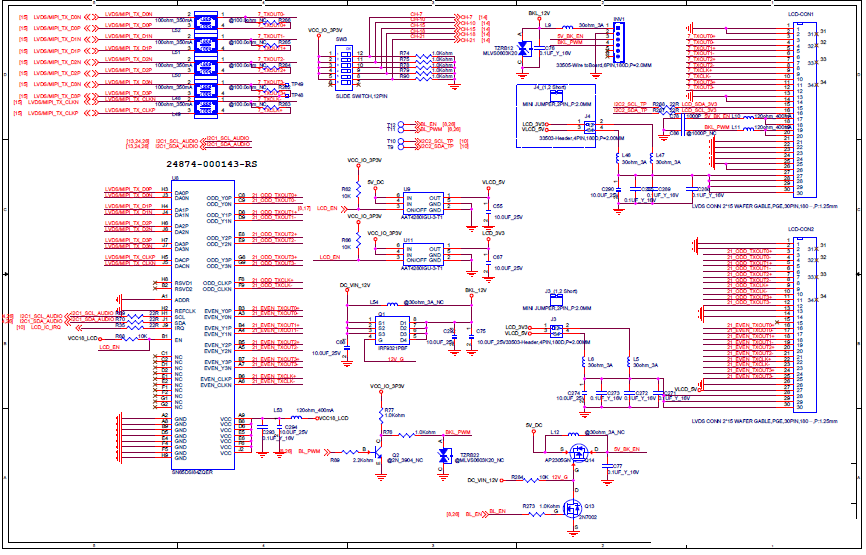

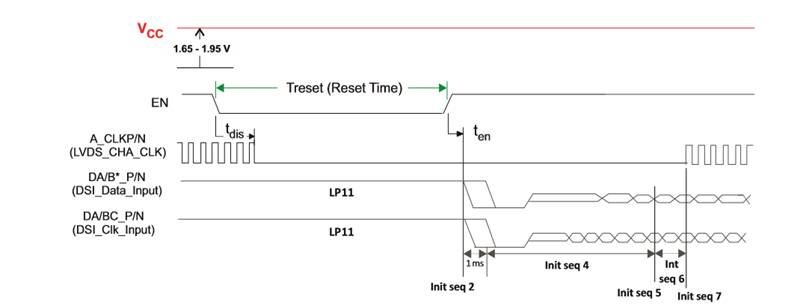

Our schematic:

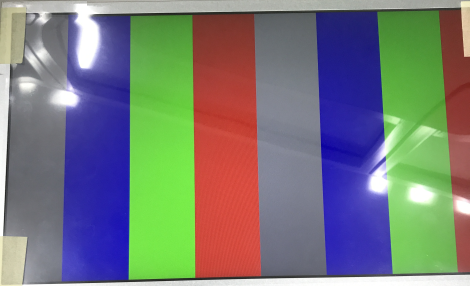

By the way, DSI84 Test Pattern was pass.

Thanks!!