Other Parts Discussed in Thread: XIO2001

We using the XIO3130 on our PCB for our new product, and hope to go to production shortly.

We have built several PCBs ( > 20 ) but we have two boards with the same intermittent problem.

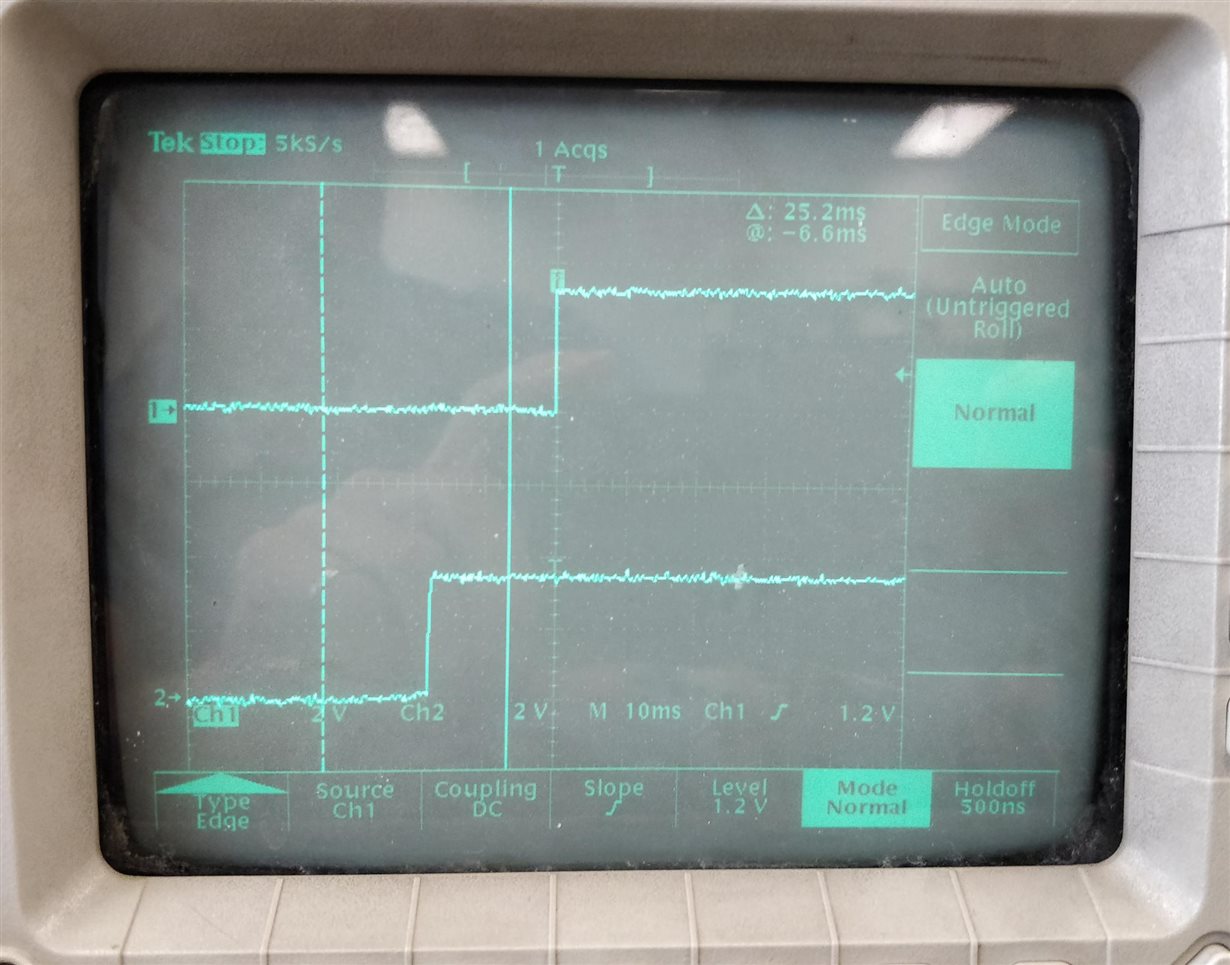

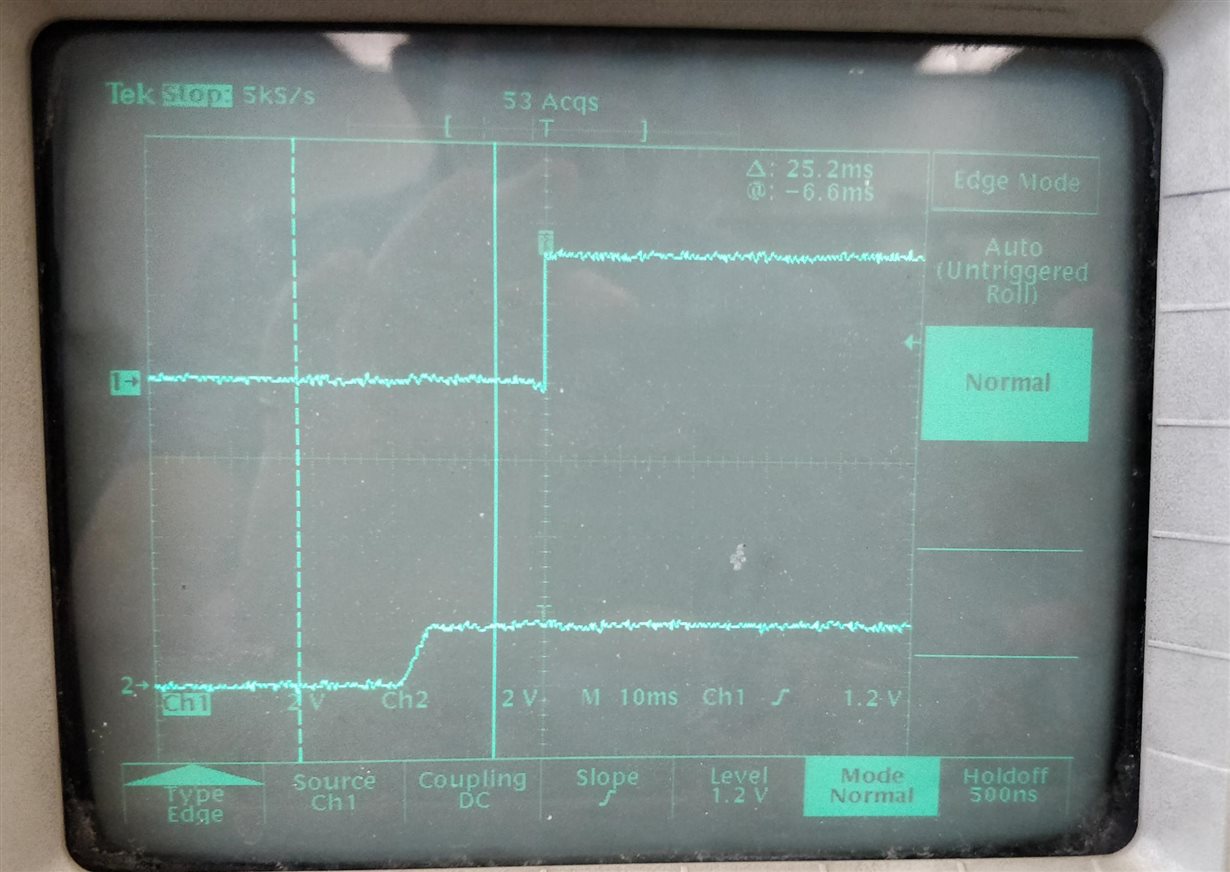

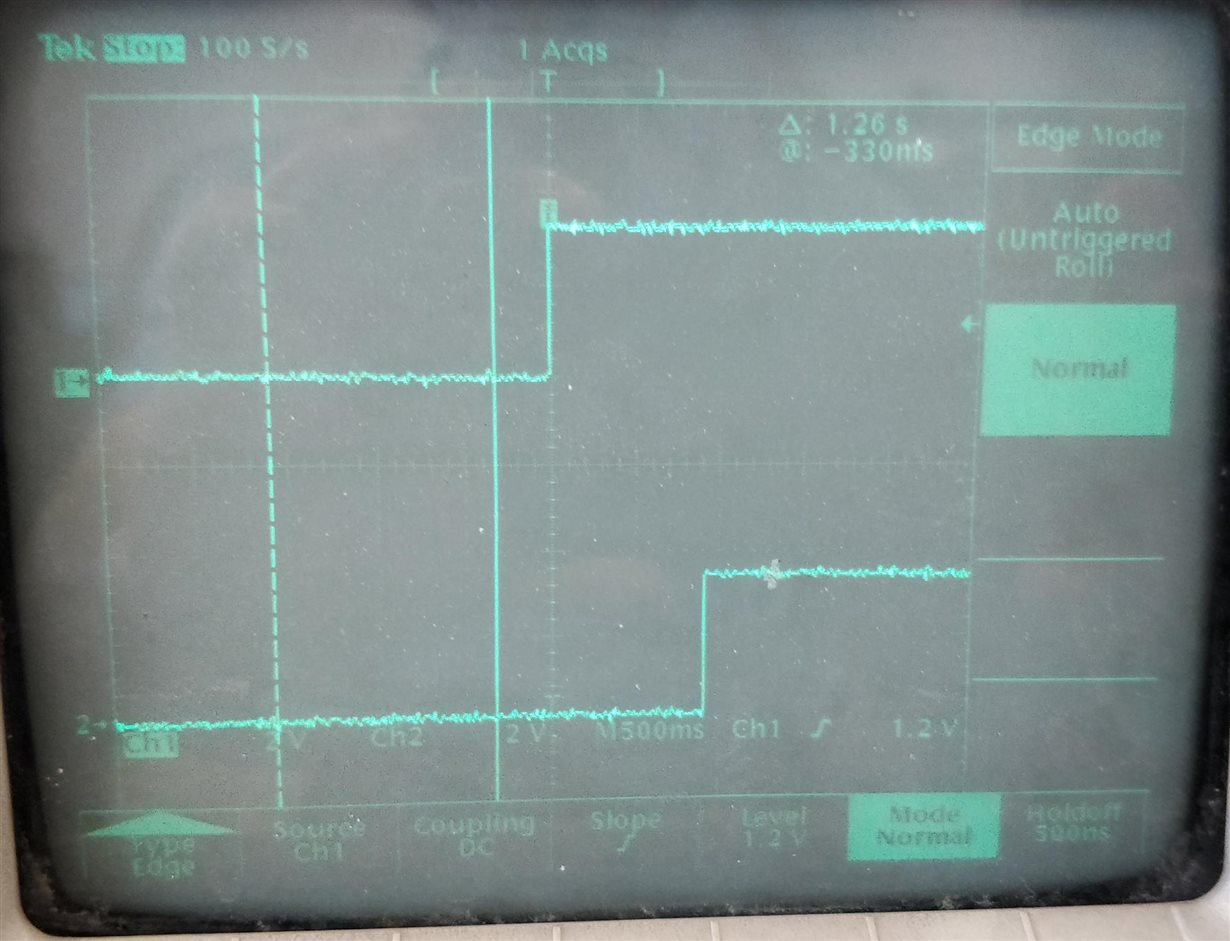

We have strapped all 3 downstream ports for PCI hotplug (DNX_DPSTRP pulled high), but sometimes do not see the PWRON# handshake signal (nor downstream PCI refclk).

This does not seem to be a power-up only issue, since under software control I have tried toggling the UP_PERST# line with the same intermittent results.

We don't use the EEPROM option, but as an experiment I enabled that feature. Again if I probe the SCL / SDA lines sometimes after reset there is no activity on these lines.

I have verified (and experimented with different input levels) the signal condition of 100 MHz PCI reference clock delivered to the XIO3130.

The +3V3 and +1V5 are ferrite-bead filtered as recommended.

Please help me narrow in on this problem before we release our product, thanks.