Hi dear supporting team,

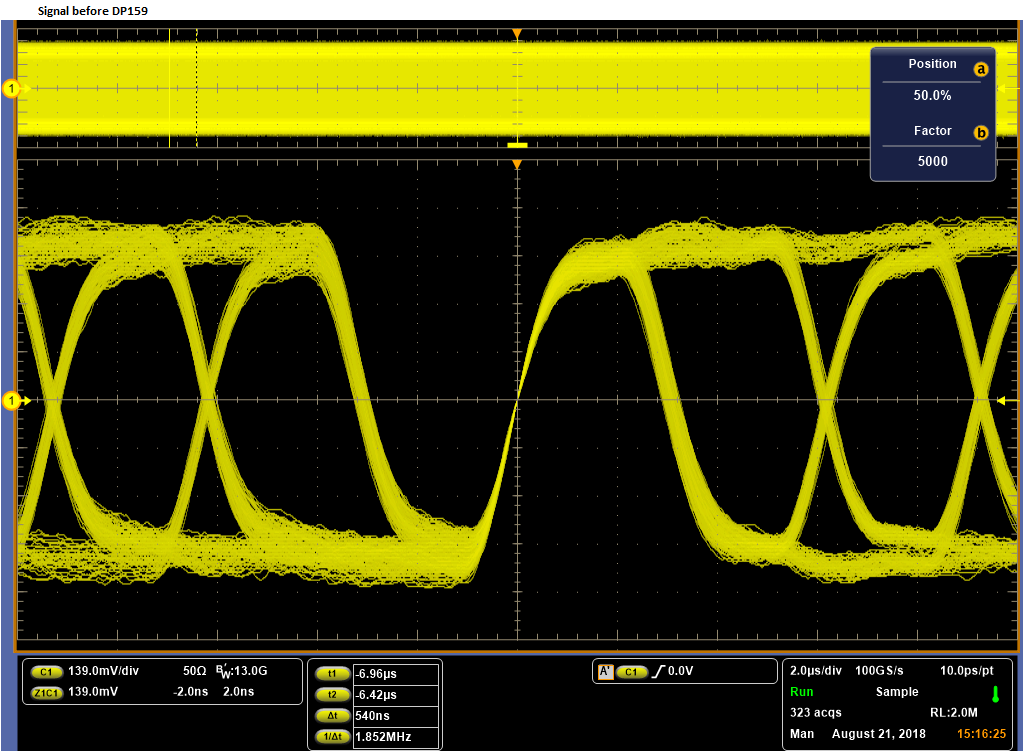

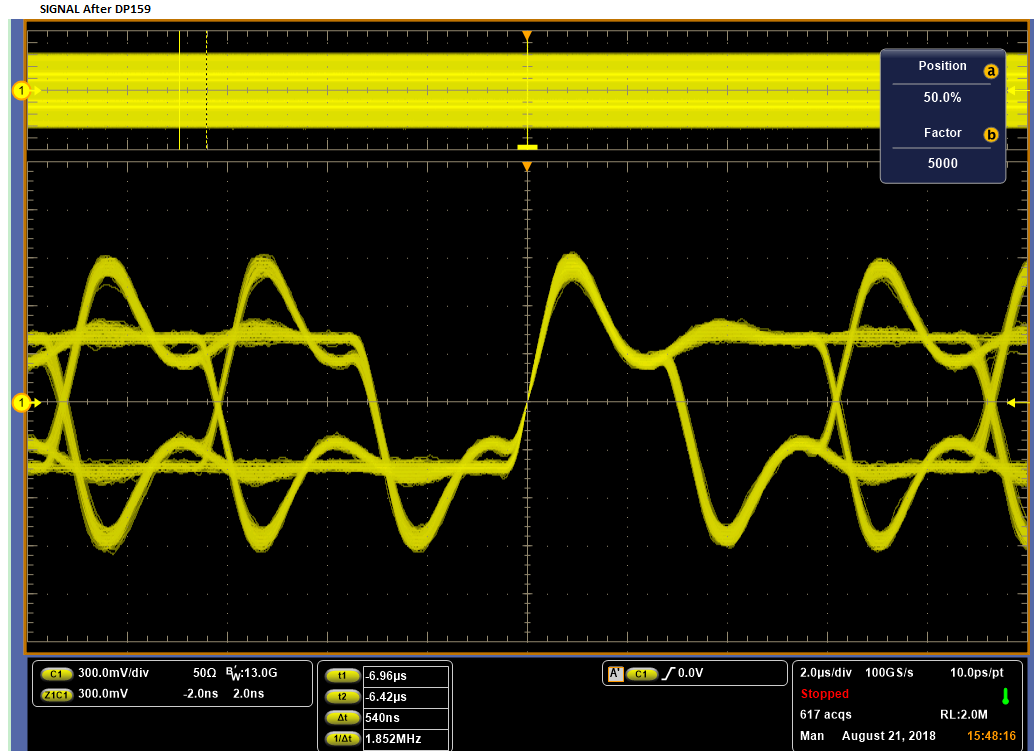

when customer using SN65DP159 displayport SINK, they set DP159 in retimer mode, but in TP1 stage, they will find PLL LOCK_COMPLETE is not set to 1, and

BERT_CNT[7:0] reg(BERT error count. Lane 0) is not 0, could you pls help suggest how to do trouble shooting?tks!