HI,

I fond this IC (TPS12S016) and I want to use it, but I'm not shore if I can.

Here is my application:

For HDMI SDA and HDMI SCl I'm using TCA9406 input site 1.8V and output site 5V (HDMI)

Question 1: on thic chpi si conected on the hdmi site on SDA and SCL line pull-up resistor(2.2kohm) in series with shotkey diode(PMEG3020EH), what is the meaning?

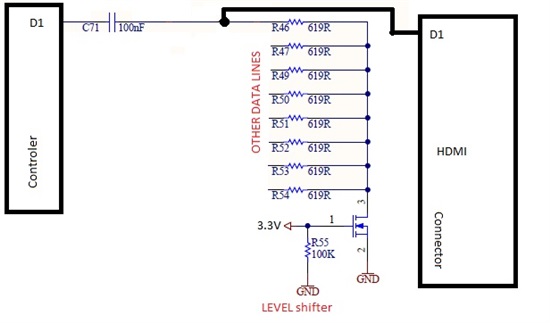

For Data0+,Data0-,Data1+,Data1-,Data2+,Data2-,clk+,clk- Signal level shifter are used resistors and one NMOS like on attached picture.

Question 2: How is this configuration working and does the TPD12S016 does the same?(level on the controler side not shore maybe 1.8V)?

Question 3: Does the IC TPD12S016 has an current limit switch like this

http://diodes.com/datasheets/AP2331.pdf

and ESD EMI protection like this

http://www.littelfuse.com/~/media/electronics/datasheets/tvs_diode_arrays/littelfuse_tvs_diode_array_sp3010_datasheet.pdf.pdf

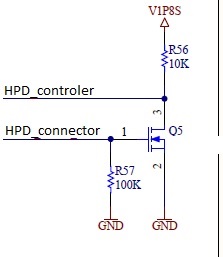

and HOT plug detection to replace this:

Question 4: DO I have to use series capacitor 100nF for data lines when using the TPD12S016?

Best Regards.