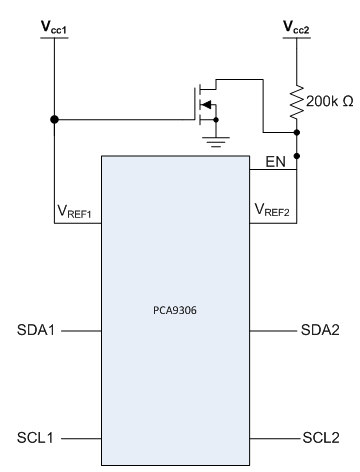

Ihave a customer using the PCA9306 as a level translator. They want to know if there are any sequencing requirements beteewn the VREF pins.

They expect there to be a condition where VREF2 will be at 3.3V for a long time before VREF1 comes up to 1.8V.