Hi Community,

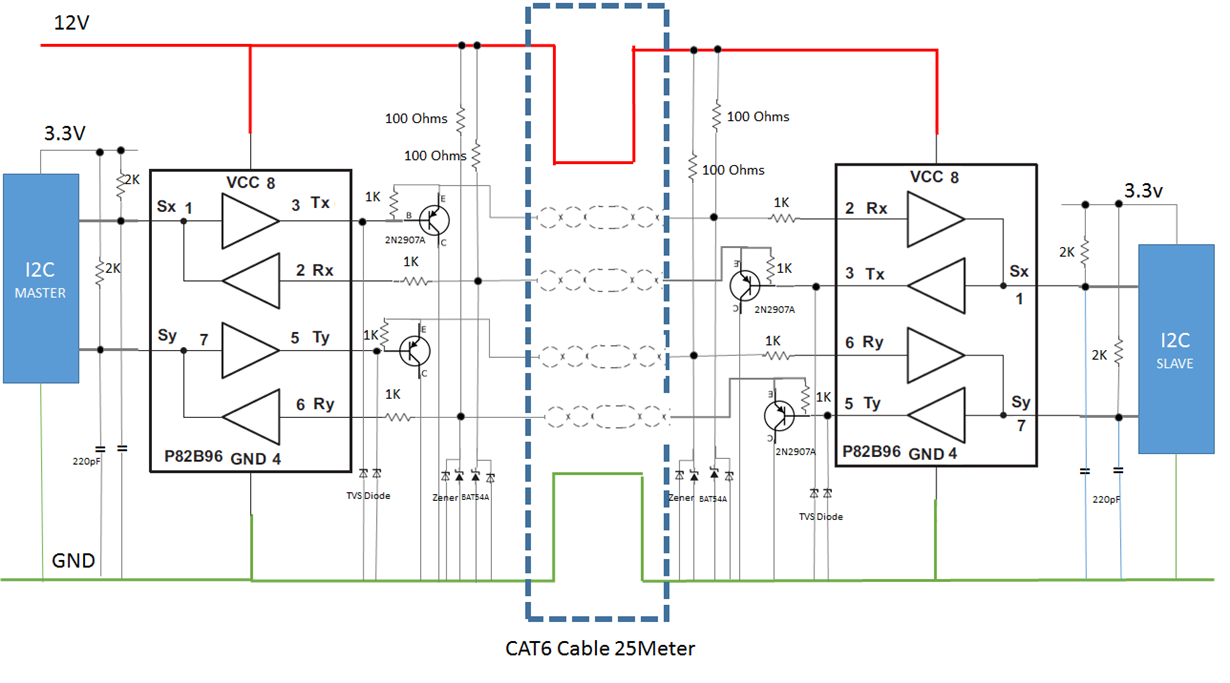

We are unable to establish I2C communication using P82B96 over 25 meter CAT6 cable. I have attached our detailed connection diagram. The lines are at 12V (sensing 10.86V only due to cable voltage drop). The MCU's on either sides are EFM32 series MCUs from Silicon Labs. The connections in diagram are similar to the ones suggested in P82B96 Data Sheet except the PNP Transistor. The PNP transistors here act as current sinks on lines, there by both enabling relatively higher current transmissions on CAT6 lines (faster transmission rates) and protecting P82B96 Tx pin from high current.

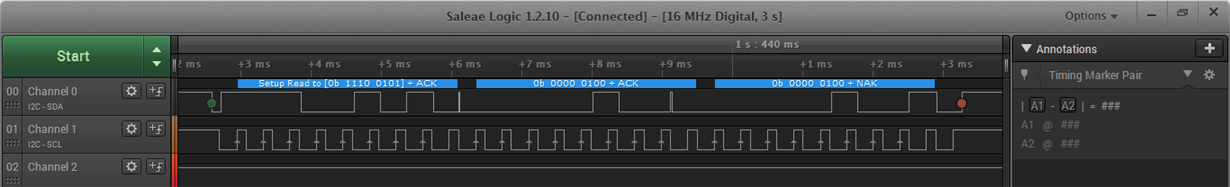

I2C communication between the MCUs is working fine with jumper wires (MCU's pins connected directly using 15cm wires) - so no program issue.

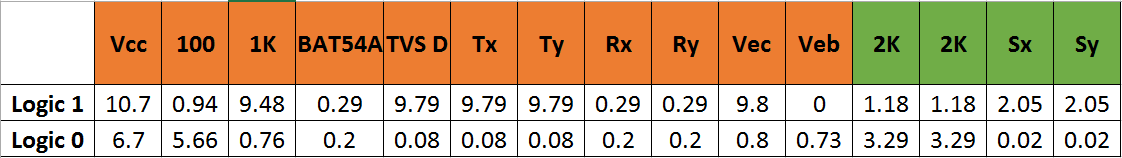

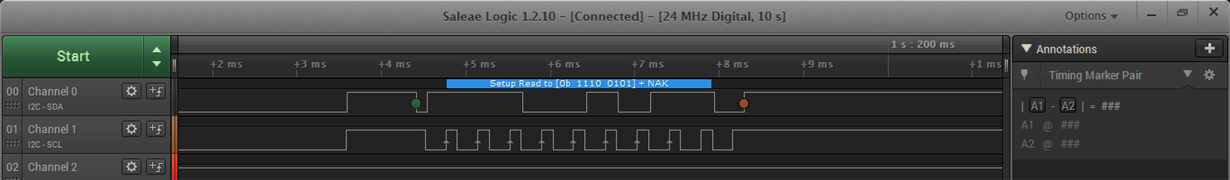

We tried various bus clock speeds - 400, 100, 30, 3 kHz, but no luck. We broke our oscilloscope and it will take a while before we can test the receive signals on scope. So, we tested the P82B96 pin voltages on either side of CAT6 cable by setting the MCU pins to high and the readings are below (readings are same for P82B96 on either sides of cable),

1) Sx and Sy pins are at constant 0.66V when the MCU pins are high(3.3V) and at 0V when MCU pins are low(0V)

2) Rx and Ry pins are at constant 0.3V when the MCU pins are high and at 0V when MCU pins are low

3) Tx and Ty pins are at 9.85V

4) P82B96 Vcc pin is at 10.86V

5) Voltage Across Transistor Emitter-Collector 9.86V

The voltages on Sx and Sy pins are at constant 0.66V even though they are pulled-high to 3.3V using 2kOhms pull-ups and MCU pins are driving high (3.3V). According to P82B96 datasheet, "The VOL level of 0.8V is needed to avoid locking/latching both sides of the P82B96 in a low state". Is the voltage locked at 0.66V because of this.

But at a 3.3V power supply, the EFM32 MCUs Input logic levels are 0.99V Max for Logic Low and 2.31V Min for Logic High. So, we suspect the logic high of P82B96 Sx pin is read as Logic Low by MCU. Does this explain why the connection is failing?

Also, even though the Rx and Ry pins are pulled high to 12V using 100 Ohms resistors, the voltage levels on pins is 0.3V. Is this expected? For the 100 Ohms pull-up resistor on these pins, the voltage on line side pin is 9.86V and voltage on Rx side pin 0.3V. So, is P82B96 internally pulling the voltage on these lines low? We checked the diode connections and they are well reverse biased and not shorted.

Could anyone please verify the voltages and let us know if they are as expected? Also, kindly suggest what could be wrong in our connection. We can run more tests and share details if required. Any help is highly appreciated.

Thanks,

Ravi