Team Please help me with a part recommendation

Situation

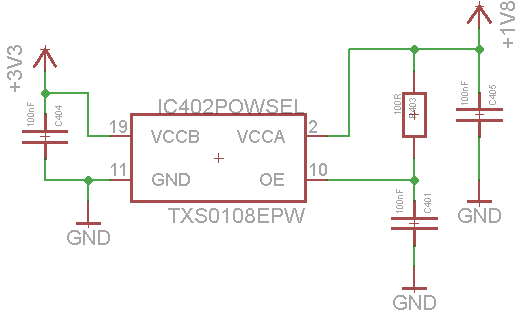

Customer has used the TXS0108E for interface between power supply status signals running at 3.3V to 5V and an FPGA that runs at 1.8V.

They found out that the TXS0108E oscillates when the signal rise/fall time is very slow. They need to replace this buffer with one that can manage both the level translation ( from 3.3V or 5V to 1.8V ) and the slow input rise/fall times as the FPGA requires fast rise/fall times on its inputs.

Details on part needed

- Buffer with 8 inputs and 8 outputs like the TXS0108E

- Input signal is open drain

- Data rate is very low speed; these are status signals coming from a power supply module, so close to DC operation

- both the level translation ( from 3.3V or 5V to 1.8V )

- Slow input rise/fall times as the FPGA requires fast rise/fall times on its inputs.

I was thinking to suggest the SN74LVCH8T245 please let me know your thoughts on this or if you can suggest a more suitable part.

Thank you!!

Antony C.