Team,

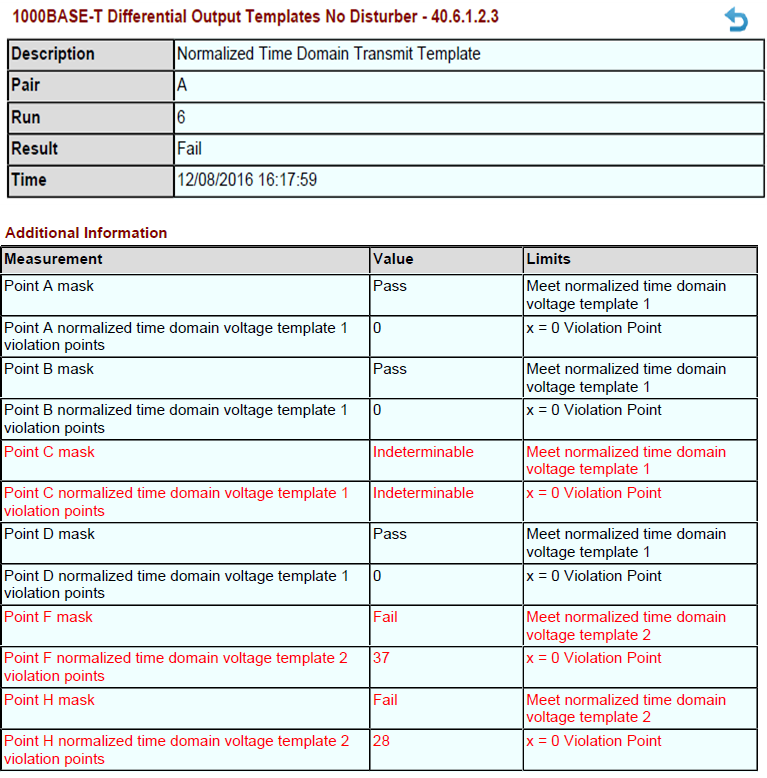

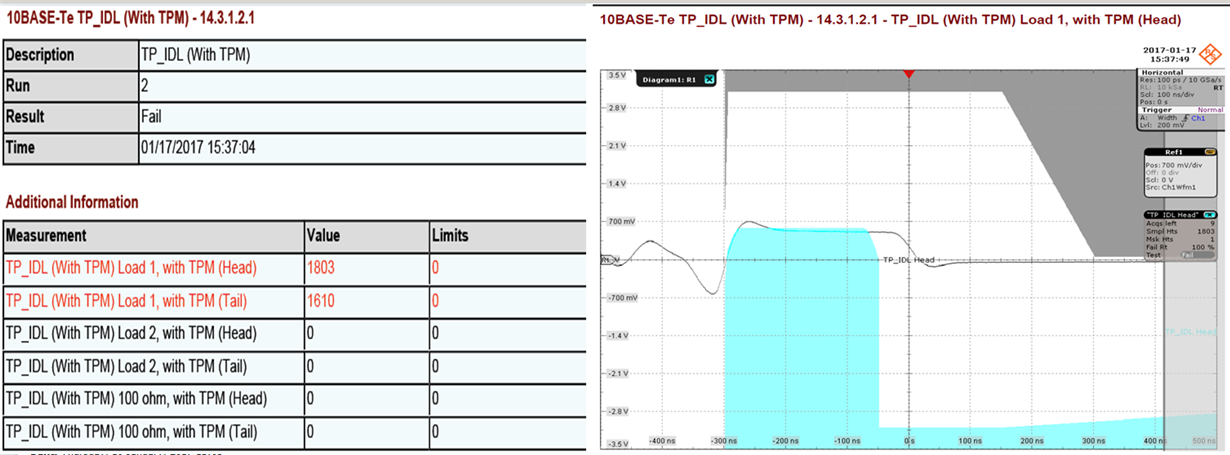

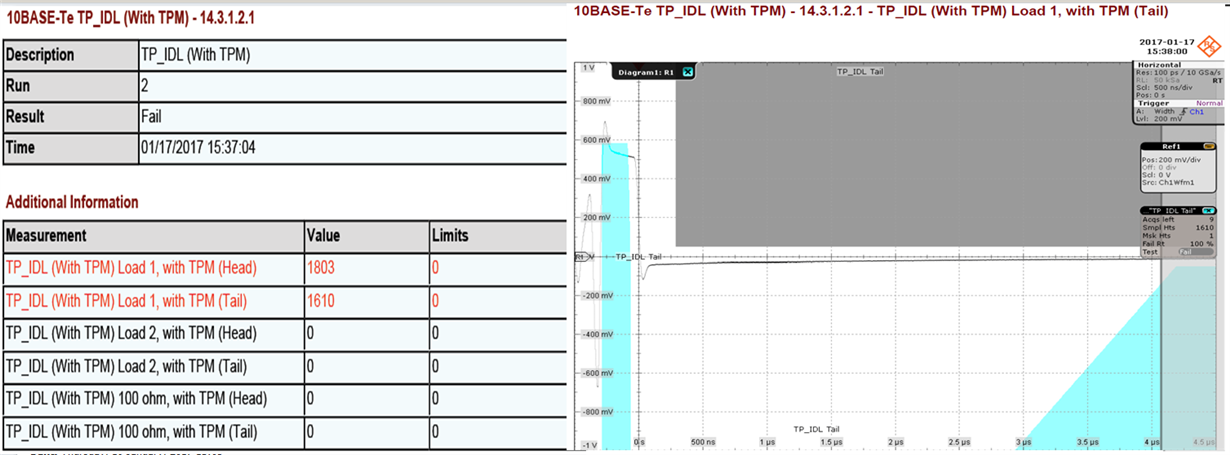

We got the feedback that some of the compliance test do fail on the DP83867 EVM ( http://www.ti.com/tool/dp83867irpap-evm ).

Testing is done using R&S RT01024 oscilloscope, RTO-K22 test SW and RT-ZF2 fixture

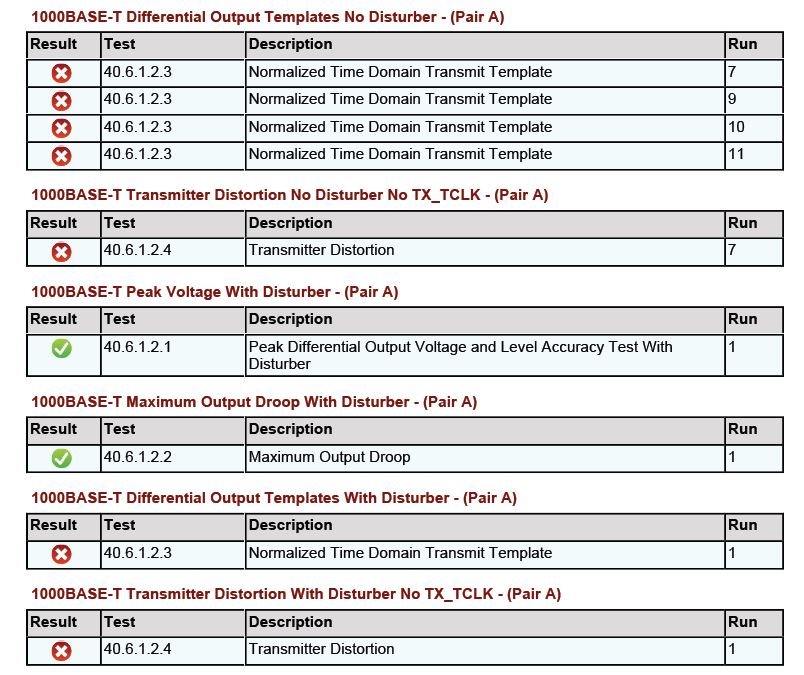

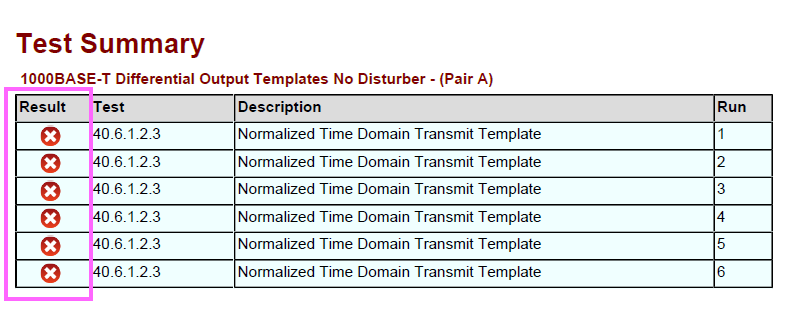

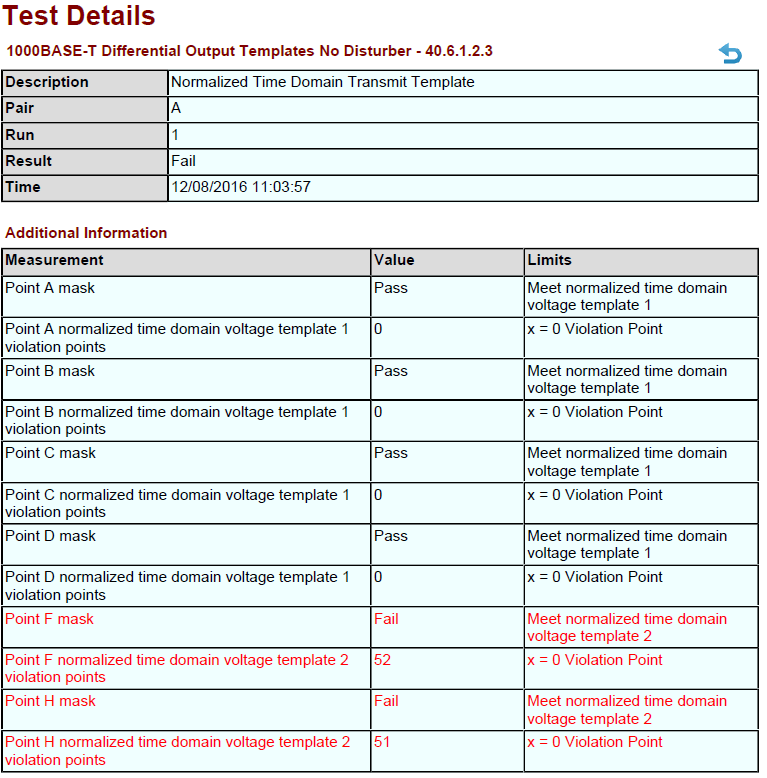

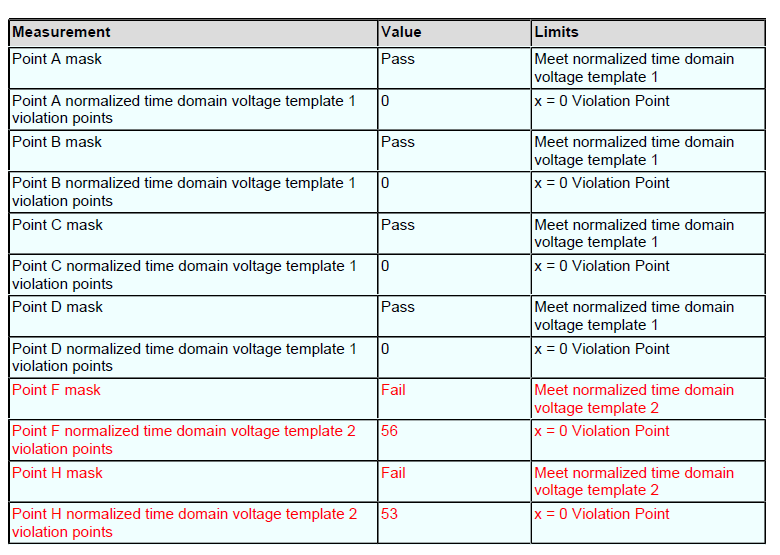

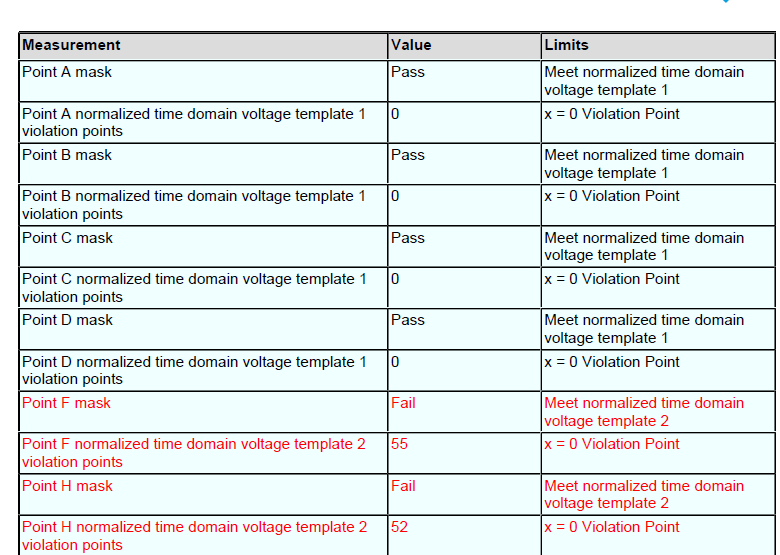

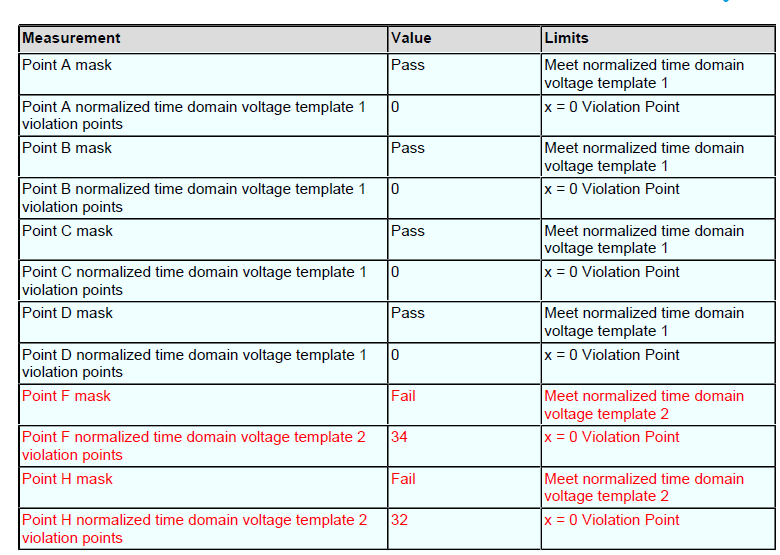

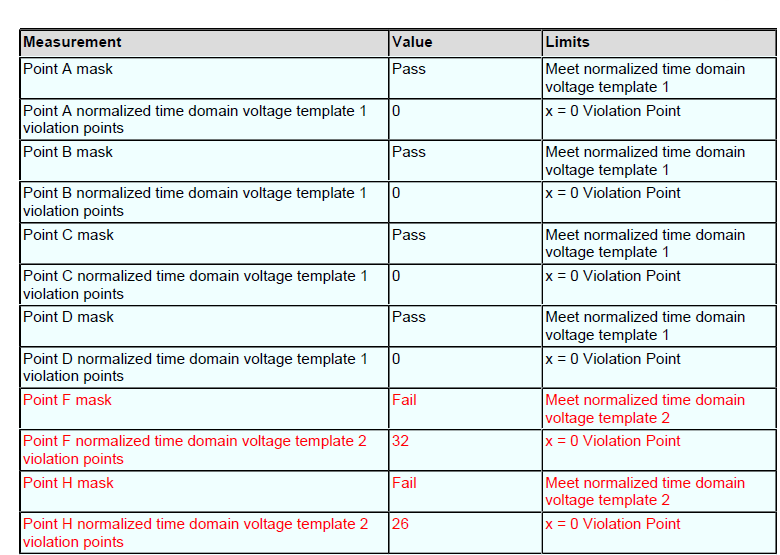

The failing test are listed below.

-Any reasons why those test would fail on the EVM?

-Are there some external condition that might influence the testing?