Dear Sir

I uesed TI CPU AM335X and DP83848Q-Q1 in my new project.

But some issue happend. DP83848 can't connumicate when the status of the register is normal.

Could you please help to give me some proposal?

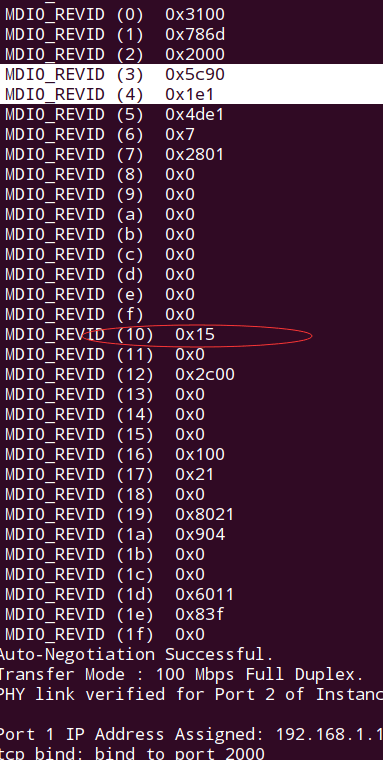

As the attactment is the SCH and Register .