Hello,

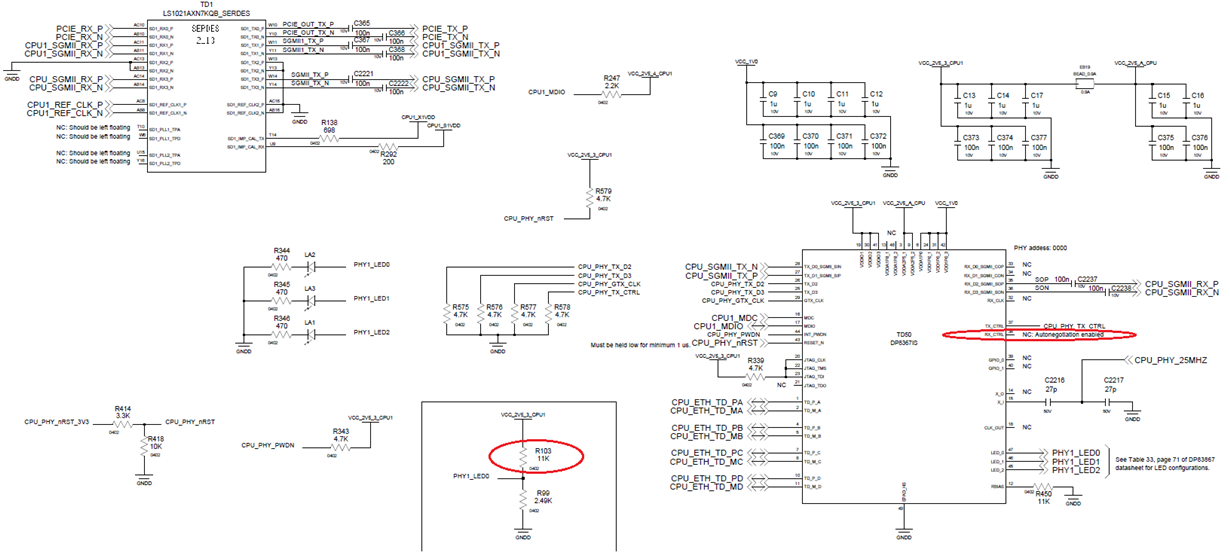

We are trying to establish communication between Freescale QorIQ LS1021 ETSEC Ethernet Controller and DP83867 PHY. They are connected through 4 wire SGMII interface. Unfortunately we started our design with the older version of DP83867 datasheet (OCTOBER 2015). Initial design can be seen from the attached DP83867_schematic file.

Then we made the following modifications in the circuitry according to the revised version (March 2017) of DP83867:

- RX_CTRL is modified to Mode3 to enable autonegotiation.

- LED_0 Rhi resistor value is changed from 11K to 10K to set strap configuration to Mode2.

In our tests we observed that in far end (reverse) loopback mode, we successfully received transmitted packages. Hovewer neither in MII loopback mode, nor in Digital loopback mode, we could not receive none of the transmitted messages. We have checked SGMII lines and observed 1.25GHz signals at transmit and receive lanes.

We have also set bit7 of register 0x31 to 0 and restarted autonegotiation by writing 0x1200 to register 0. But we did not observe any improvement.

Dumped DP83867 register values are given below.

Do you have any suggestions to solve SGMII autonegotiation problem?

Kind Regards,

Asil YILDIRIM

RX_D0 and RX_D2 are at Mode1, so PHY address is 0.

register 0x31 kept unchanged:

phy add 0

reg add: 0x00000000, val: 0x00001000

reg add: 0x00000001, val: 0x0000796d

reg add: 0x00000002, val: 0x00002000

reg add: 0x00000003, val: 0x0000a231

reg add: 0x00000004, val: 0x000001e1

reg add: 0x00000005, val: 0x0000c1e1

reg add: 0x00000006, val: 0x0000006d

reg add: 0x00000007, val: 0x00002001

reg add: 0x00000008, val: 0x00004806

reg add: 0x00000009, val: 0x00000300

reg add: 0x0000000a, val: 0x00003800

reg add: 0x0000000b, val: 0x00000000

reg add: 0x0000000c, val: 0x00000000

reg add: 0x0000000d, val: 0x0000401f

reg add: 0x0000000e, val: 0x00000095

reg add: 0x0000000f, val: 0x00003000

reg add: 0x00000010, val: 0x00005848

reg add: 0x00000011, val: 0x0000ae02

reg add: 0x00000012, val: 0x00000000

reg add: 0x00000013, val: 0x00000000

reg add: 0x00000014, val: 0x000029c7

reg add: 0x00000015, val: 0x00000000

reg add: 0x00000016, val: 0x00000000

reg add: 0x00000017, val: 0x00000040

reg add: 0x00000018, val: 0x00006150

reg add: 0x00000019, val: 0x00004444

reg add: 0x0000001a, val: 0x00000002

reg add: 0x0000001b, val: 0x00000000

reg add: 0x0000001c, val: 0x00000000

reg add: 0x0000001d, val: 0x00000000

reg add: 0x0000001e, val: 0x00000002

reg add: 0x0000001f, val: 0x00000000

phy add 0

reg add: 0x00000025, val: 0x00000400

reg add: 0x00000031, val: 0x000010b0

reg add: 0x00000032, val: 0x000000d3

reg add: 0x00000033, val: 0x00000000

reg add: 0x00000037, val: 0x00000001

reg add: 0x00000038, val: 0x00000000

reg add: 0x0000006e, val: 0x00000800

reg add: 0x0000006f, val: 0x00000100

reg add: 0x00000071, val: 0x00000000

reg add: 0x00000072, val: 0x00000000

reg add: 0x000000d3, val: 0x00000000

reg add: 0x000000dc, val: 0x00003800

reg add: 0x000000fe, val: 0x0000e721

reg add: 0x00000135, val: 0x00000000

reg add: 0x0000016f, val: 0x00000095

Register 0x31 bit7 is set to 0:

phy add 0

reg add: 0x00000000, val: 0x00001000

reg add: 0x00000001, val: 0x0000796d

reg add: 0x00000002, val: 0x00002000

reg add: 0x00000003, val: 0x0000a231

reg add: 0x00000004, val: 0x000001e1

reg add: 0x00000005, val: 0x0000c1e1

reg add: 0x00000006, val: 0x0000006d

reg add: 0x00000007, val: 0x00002001

reg add: 0x00000008, val: 0x00004806

reg add: 0x00000009, val: 0x00000300

reg add: 0x0000000a, val: 0x00003800

reg add: 0x0000000b, val: 0x00000000

reg add: 0x0000000c, val: 0x00000000

reg add: 0x0000000d, val: 0x0000401f

reg add: 0x0000000e, val: 0x00000095

reg add: 0x0000000f, val: 0x00003000

reg add: 0x00000010, val: 0x00005848

reg add: 0x00000011, val: 0x0000ae02

reg add: 0x00000012, val: 0x00000000

reg add: 0x00000013, val: 0x00000000

reg add: 0x00000014, val: 0x000029c7

reg add: 0x00000015, val: 0x00000000

reg add: 0x00000016, val: 0x00000000

reg add: 0x00000017, val: 0x00000040

reg add: 0x00000018, val: 0x00006150

reg add: 0x00000019, val: 0x00004444

reg add: 0x0000001a, val: 0x00000002

reg add: 0x0000001b, val: 0x00000000

reg add: 0x0000001c, val: 0x00000000

reg add: 0x0000001d, val: 0x00000000

reg add: 0x0000001e, val: 0x00000002

reg add: 0x0000001f, val: 0x00000000

phy add 0

reg add: 0x00000025, val: 0x00000400

reg add: 0x00000031, val: 0x00001030

reg add: 0x00000032, val: 0x000000d3

reg add: 0x00000033, val: 0x00000000

reg add: 0x00000037, val: 0x00000001

reg add: 0x00000038, val: 0x00000000

reg add: 0x0000006e, val: 0x00000800

reg add: 0x0000006f, val: 0x00000100

reg add: 0x00000071, val: 0x00000000

reg add: 0x00000072, val: 0x00000000

reg add: 0x000000d3, val: 0x00000000

reg add: 0x000000dc, val: 0x00003800

reg add: 0x000000fe, val: 0x0000e721

reg add: 0x00000135, val: 0x00000000

reg add: 0x0000016f, val: 0x00000095