Tool/software: Linux

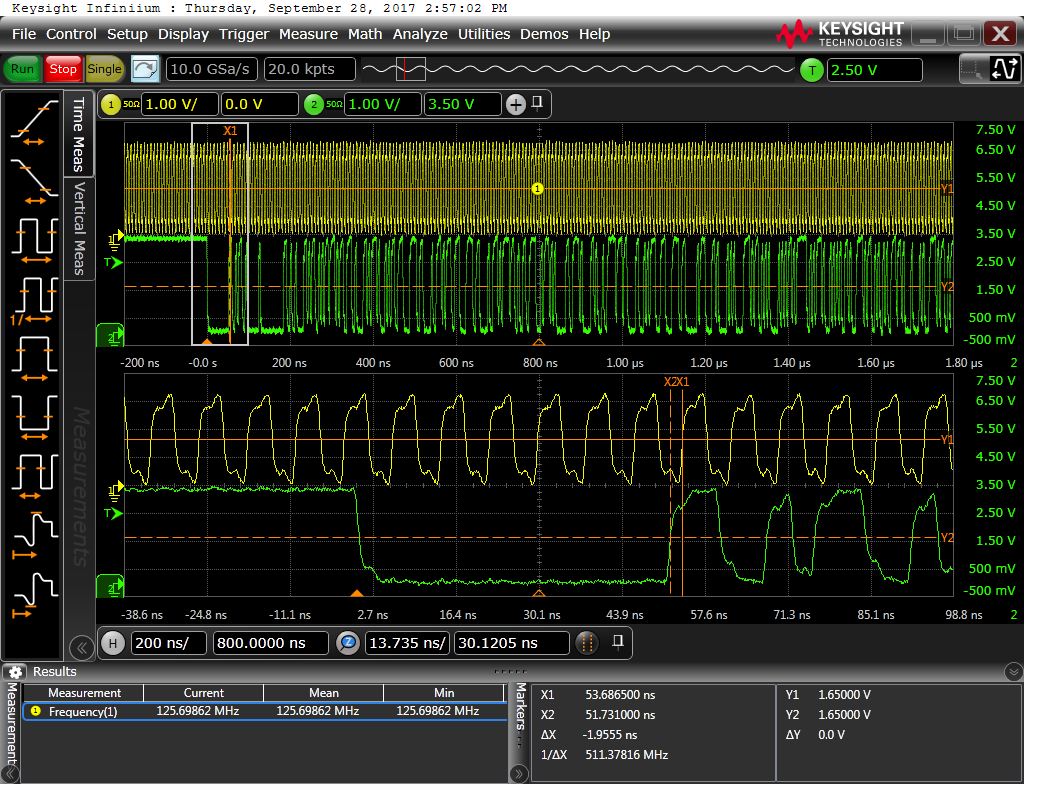

Hi, we use TI DP83867IRRGZR PHY on Rockchip RK3288 platform. The 18 pin CLK_OUT of DP83867IR need to provide 125MHz clock to meet CPU RK3288’s spec.

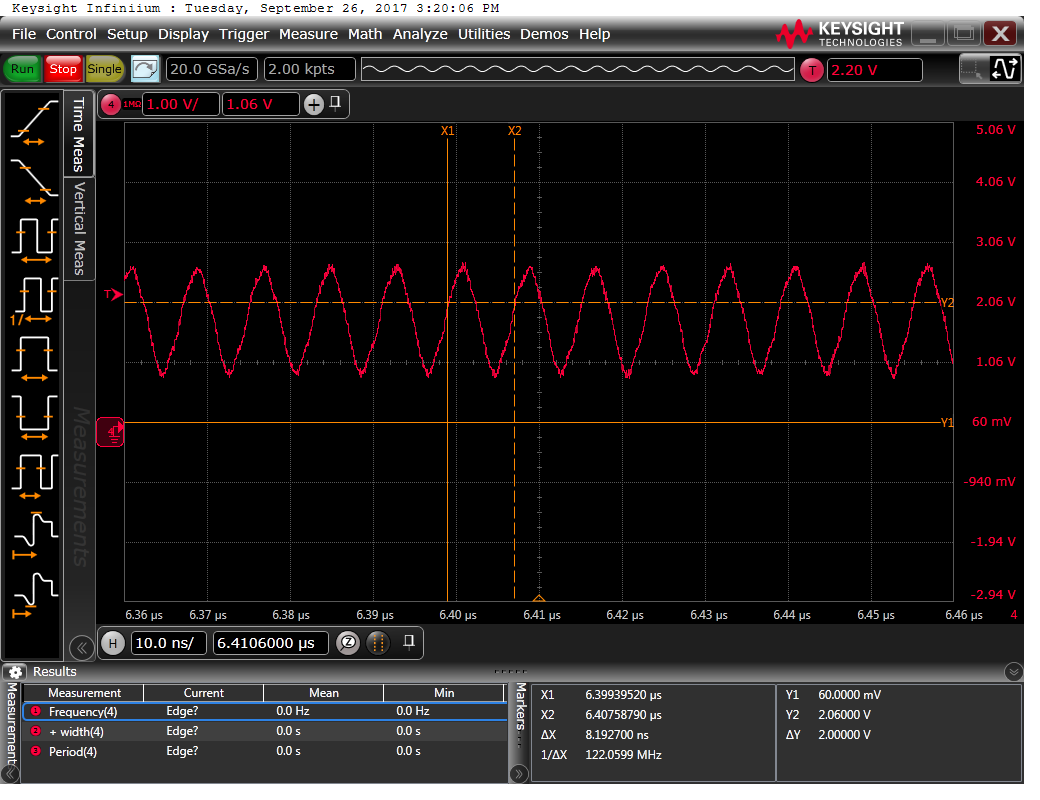

But it’s always 25MHz CLK-OUT. We had configured register[12:8](CLK_O_SEL) to 0x08,0x04,0x00, but the CLK-OUT is the same 25MHz,

and I back to read the register value, it’s my configured value.

So what can I do next? thanks!