Hi Team,

My customer is using our DP83822. They use FPGA to realize Mac function. Below is the schematic for your check, 4pcs/board.

They use RMII and 50MHz osc reference.

The problem is that:

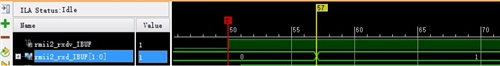

1. When debugging DP83822, it was found that the RXDV, RXD[1:0] timing from PHY may have some problem: RXD[1:0] signal will come out 7 clk(about 140ns) after RXDV signal. See below timing picture:

2. These is sudden change at the end of the RXDV's message, see below:

Customer is pushing the pp schedule, so can you help check above 2 questions, thanks a lot!

Best regards,

Sulyn