Hello,

We use the LMH1218 extensively in our product range and have been pleased with the performance of the device. However, we recently designed a product that will output SL12G video and this has highlighted a couple of problems.

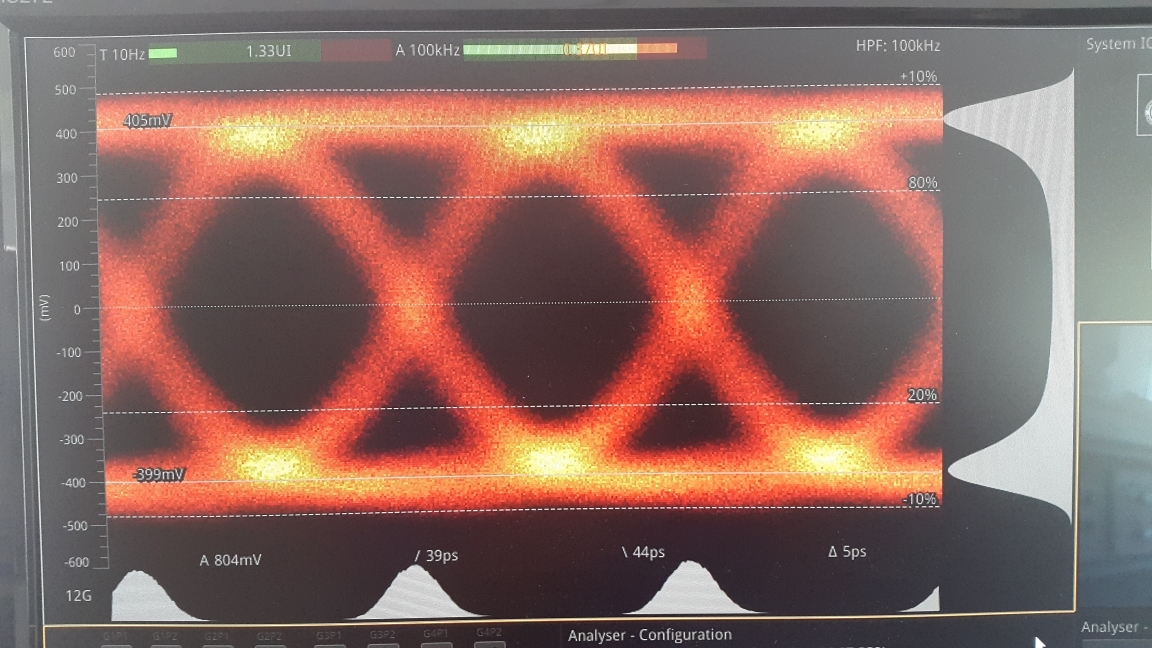

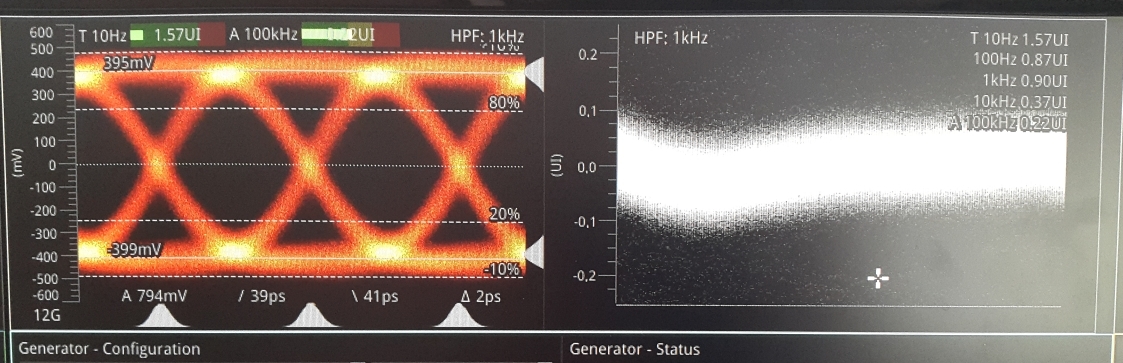

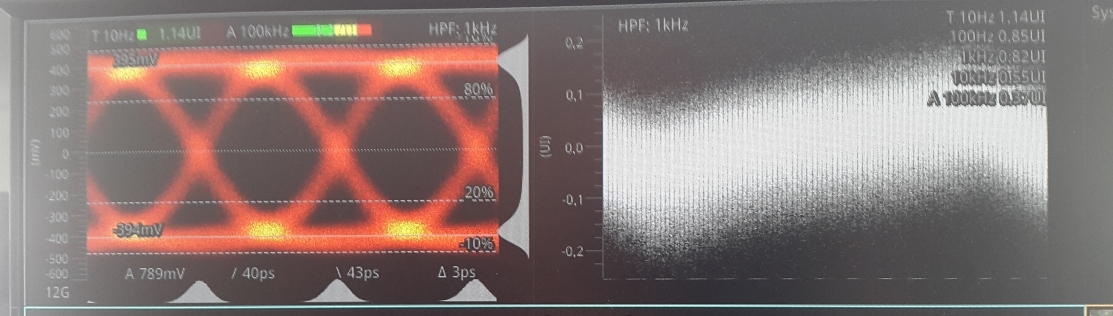

Previously we have used the device for 3G video outputs and not had any problems with video performance. On the new board with that provides a SL12G video output, the video and eye pattern are fine but we have quite high alignment jitter. On investigation we found that the LOCKED signal on pin 16 of the device is low suggesting that it is not locked to the incoming 12G and passing the video through RAW as a result without retiming/reclocking.

We checked the LMH1218 on our previous boards operating with 3G video that have good video performance and discovered that when monitoring pin 16 they are also not locked?

We know that we are writing to registers successfully as we can see the effect of changing parameters through them. When we are using 3G video we are able to adjust register OUT0_VOD (0x80.)

However, as soon as we try to set any value for register 0x80 in 12G, the output is switched off and we do not get an eye pattern?

Below are the registers we set for initialisation and control with the register 0x80 setting commented out.

{0xFF, 0x04, 0x07}, //enable channel control

{0x16, 0x25, 0xFF},

{0x3E, 0x00, 0x80},

{0x55, 0x02, 0x02},

{0x6A, 0x00, 0xFF},

{0x03, 0x00, 0xFF},

{0x0A, 0x0C, 0x0C}, // Reset CDR

{0x0A, 0x00, 0x0C}, // Release Reset

{0xFF, 0x04, 0x07}, // enable channel control

{0x31, 0x01, 0x03},

{0x2F, 0x00, 0xC0},

{0xFF, 0x04, 0x07}, // enable channel control for VOD level adjust

//{0x80, 0x44, 0xFF}, // VOD level adjust

//{0x0A, 0x0C, 0x0C}, // Reset CDR

//{0x0A, 0x00, 0x0C}, // Release Reset

{0x84, 0x03, 0x03}, // Power Down out 1

{0x0A, 0x0C, 0x0C}, // Reset CDR

{0x0A, 0x00, 0x0C}, // Release Reset

{0xFF, 0xFF, 0x00}

Could you please let me know if we are setting these correctly and in the correct format?

Thanks in advance,

John.