Hi team,

I would like to know more about the behavior when the 954 releases the clock stretch.

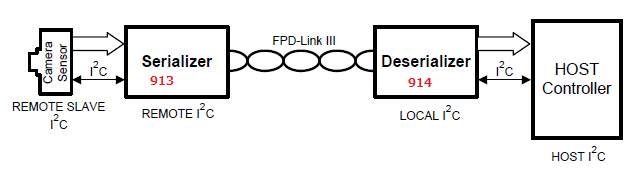

I assume the following configuration.

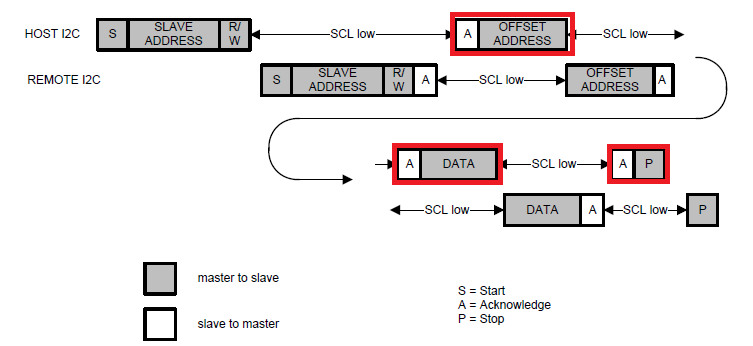

I understand clock stretching will occur on the host I2C when executing instructions to the remote slave as follows.

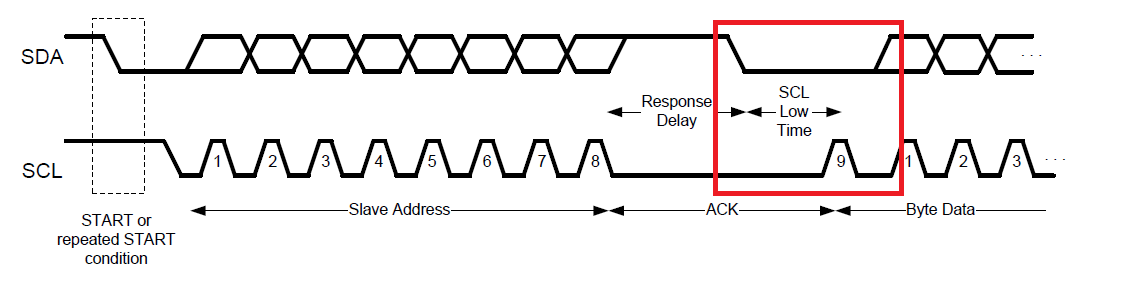

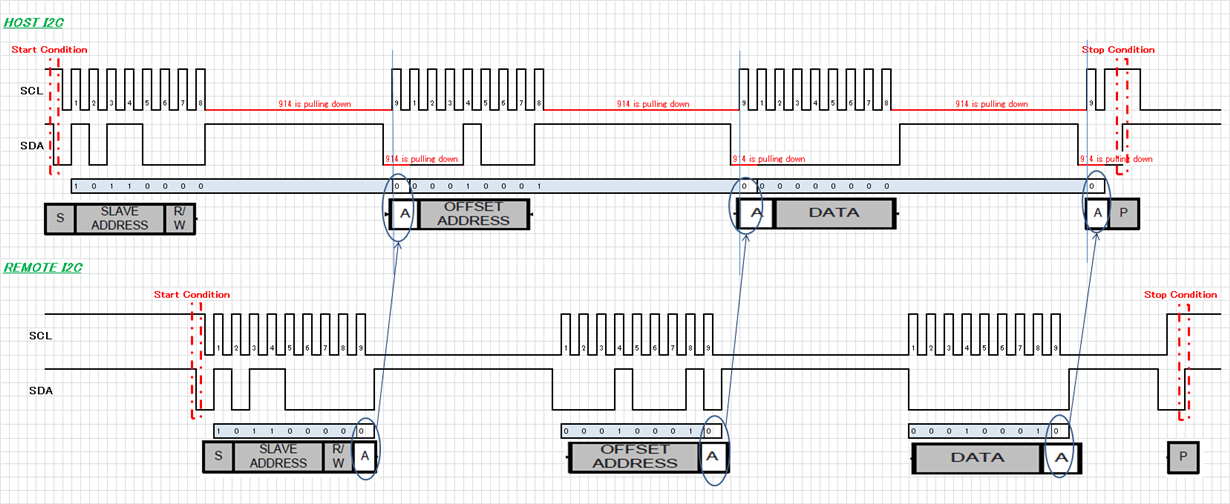

At this time, 914 is pulling down SCL and SDA is high.

I think that I2C transaction ends at remote I2C and 914 will release clock stretch when ACK or NACK returns at 914, but I want to know the behavior of 914 at that time.

If ACK is returned.

914 will pull SDA low and after a while releases SCL.

Thereafter, 914 does nothing until the host pulls SCL low.

When the host pulls SCL low, 914A also releases SDA.

That is, as long as the host does not pull SCL Low after releasing the clock stretch, the local I2C is stalled in that state.

Is it right?

Is there a possibility that 914 will change SCL or SDA after releasing clock stretch?

Best regards,

Tomoaki Yoshida