Other Parts Discussed in Thread: TMDS141, TMDS181, TUSB3410

Hi all

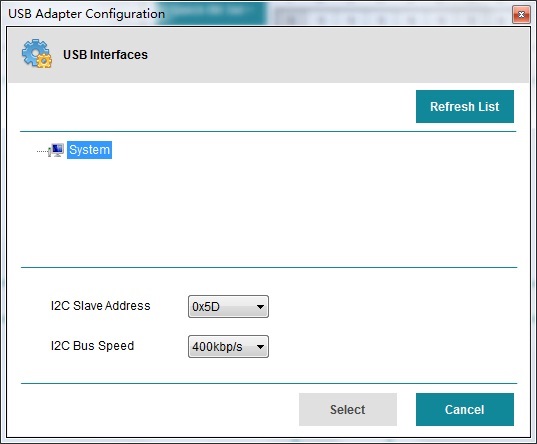

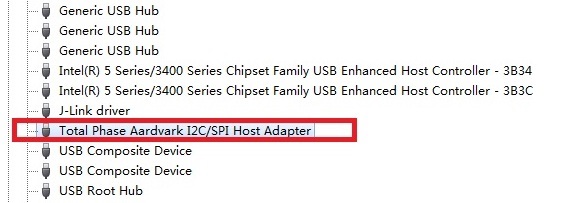

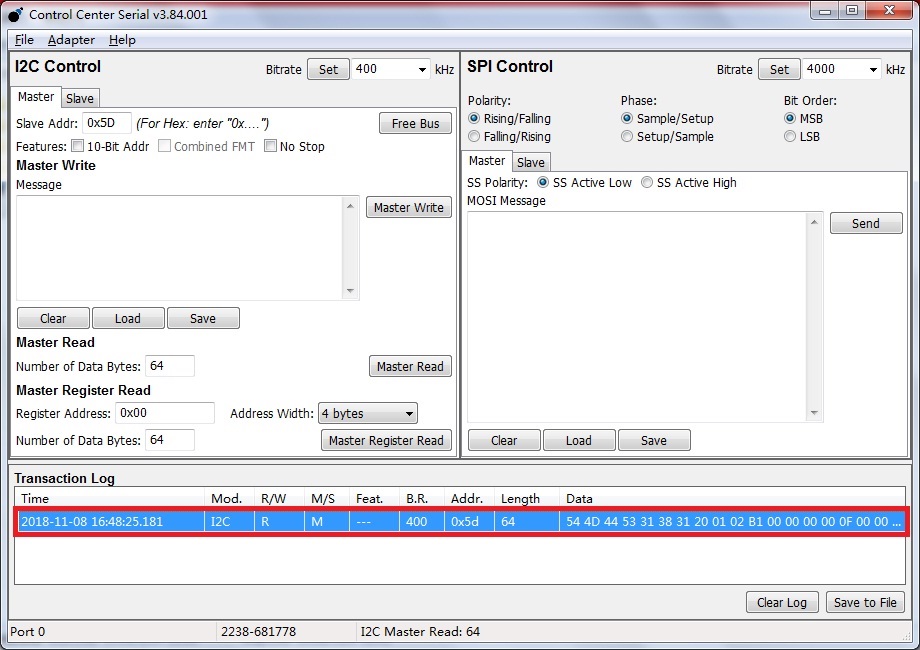

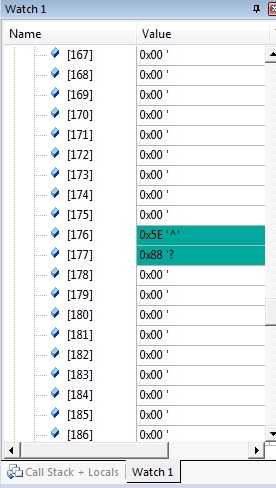

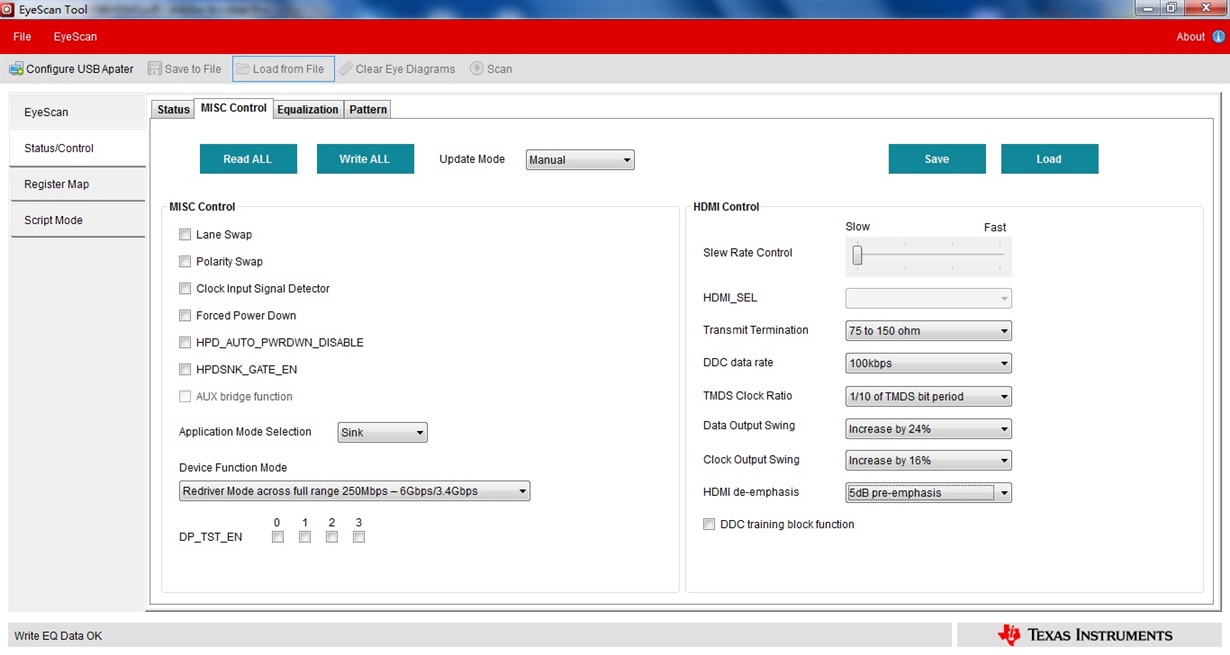

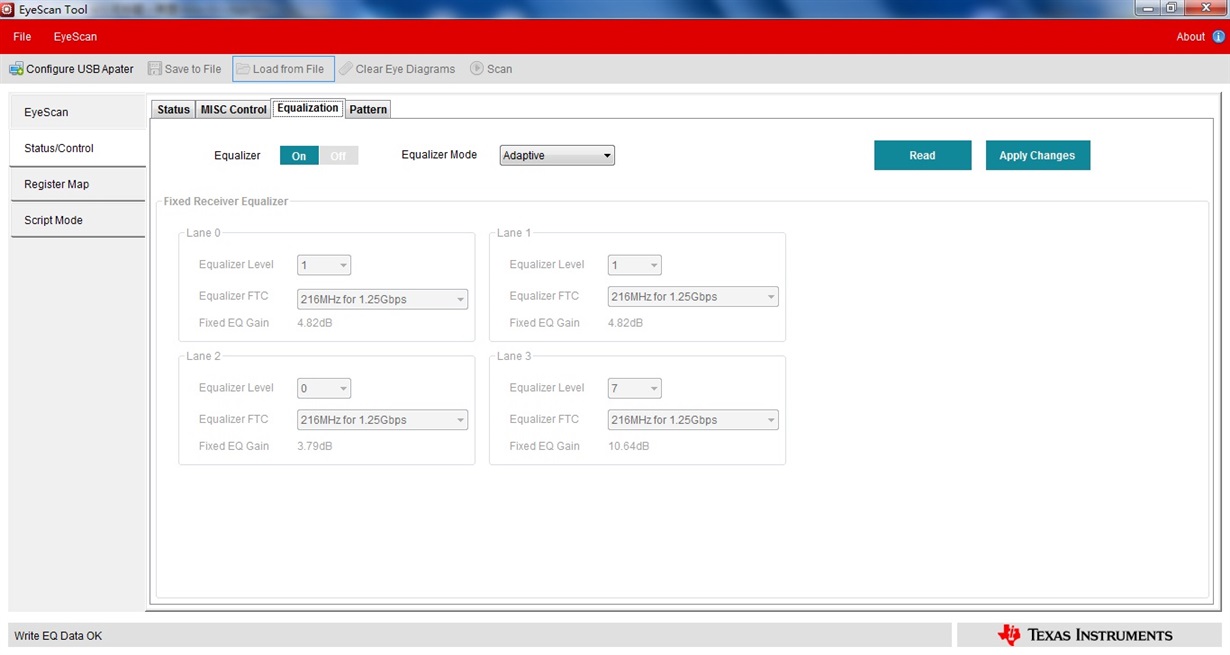

I'm using TMDS171 between HDMI connetor and FPGA,sink side.I have met just the same problem as the link shown below.The frequency of I2C clk is 100KHz

That thread has been locked without resolved.

https://e2e.ti.com/support/interface/f/138/t/680883?tisearch=e2e-sitesearch&keymatch=tmds181

Anyone could help?

Thanks!