Hi,

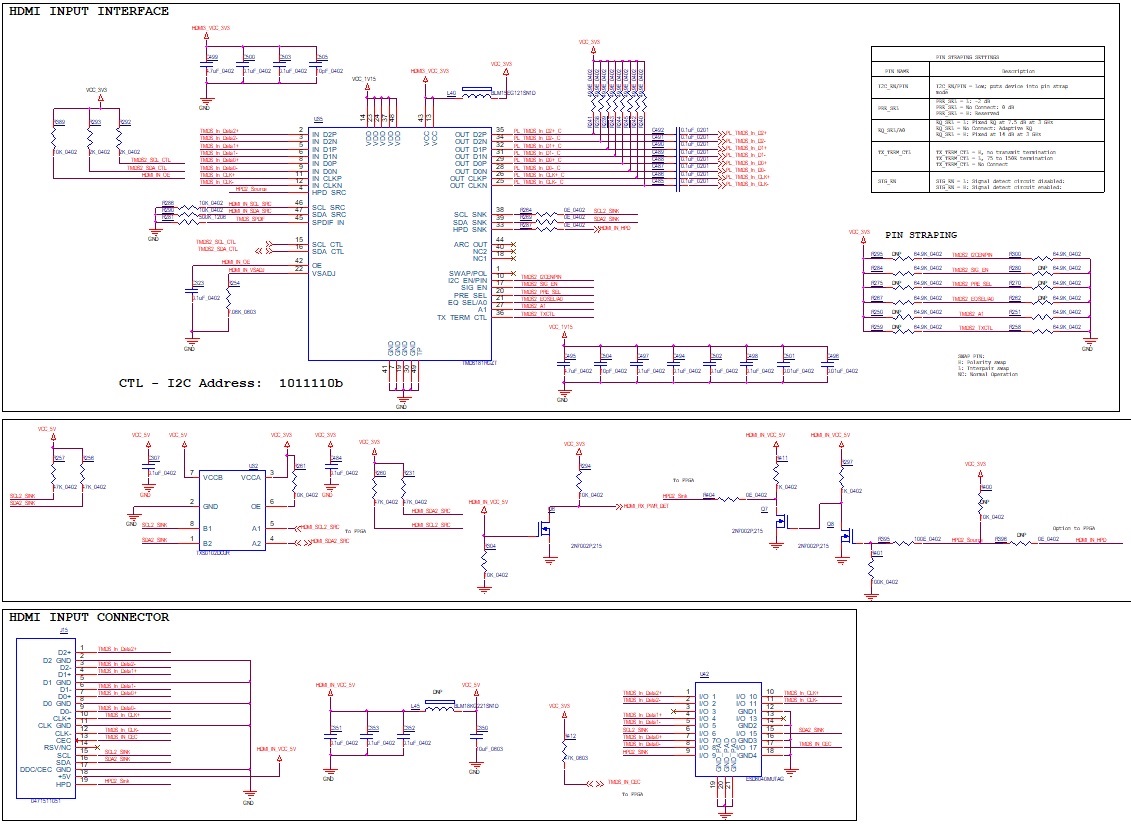

We are using the TMDS181 in Sink application with video @4K60Hz.

We have seen that when we give the input with standard hardware strappings with below settings:

I2C Enabled, Sig_En high, PRE_Sel No connection, EQ_sel high, TX_Term_ctl low

We see that in one of the boards it works fine for both @4K60Hz & @4K30Hz; In other boards only @4K30Hz is working fine and @4K60 is not coming up.

So we moved into I2C control section and we found that in working board the value of 0x0B register @4K30Hz is 0xD8 and @4K60Hz its 0xDA dynamically updated as the input changes

But in the non working boards we see that it's always 0xD8 and not updating according to the input.

when we change manually (register 0x0B with 0xDA) we see that it's working fine @4K60Hz.

What could be causing the issue in the non working board, as the settings are same on all the boards & also the input is same.

Anyone please help.

Thanks & Regards,

Nanjunda M