Other Parts Discussed in Thread: THVD1550

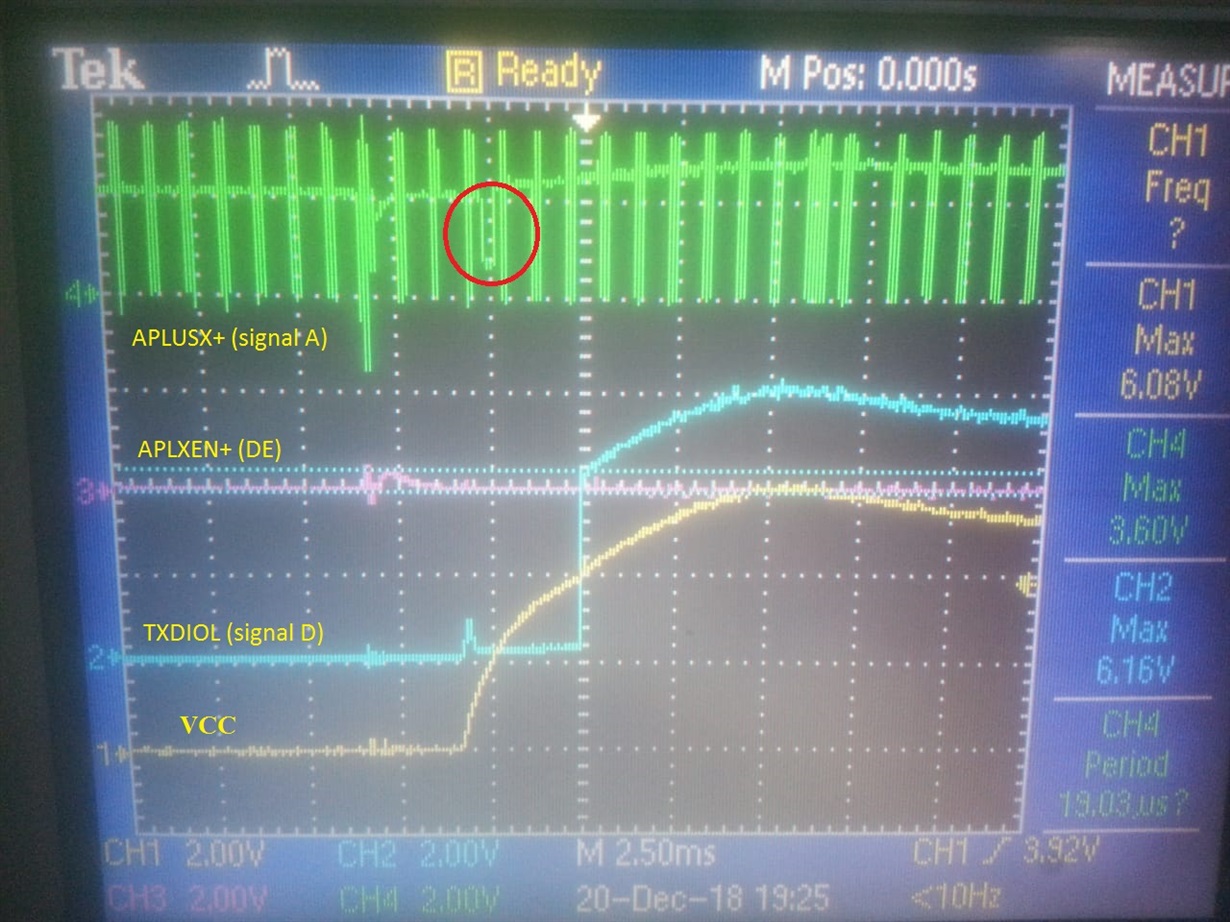

I’m using SN75176B Differential Bus Transceiver in one Input module with uC AT89S52-24U. I’m getting errors in differential RS-485 communication. I’ve attached SN75176B signals captured. I observed glitch in Communication signal (RS 485, signal ‘A’, Channel 4), when DE (Channel 3) is low, and before signal D, (channel 2) is going High, because of this condition we’re getting communication errors. This condition occurs on every Power ON state, so whenever module is inserted in system, we get error in communication.

Actually, When DE is low, till that period there should not be any impact on differential Signals ‘A’ and ‘B’.

This scenario occurs when I used AT89S52-24JU uC, but this is not observed with NXP uC P80C32 uC. I’ve attached both scenario. Can you please analyze this condition and inform us why this is happening?