Other Parts Discussed in Thread: ALP

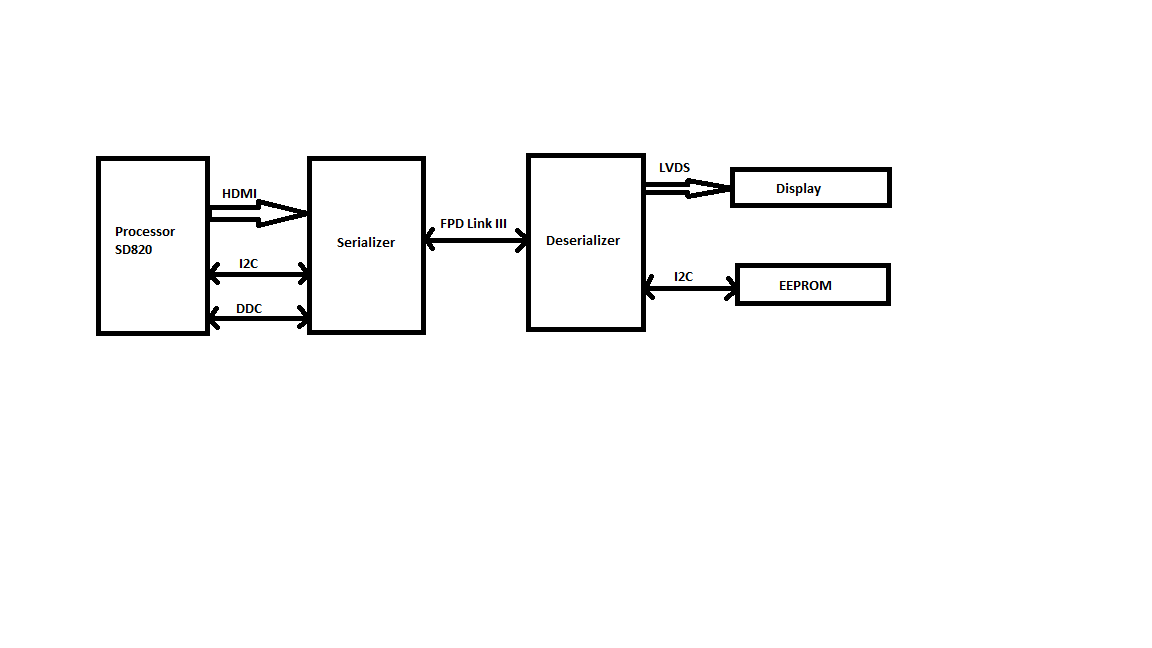

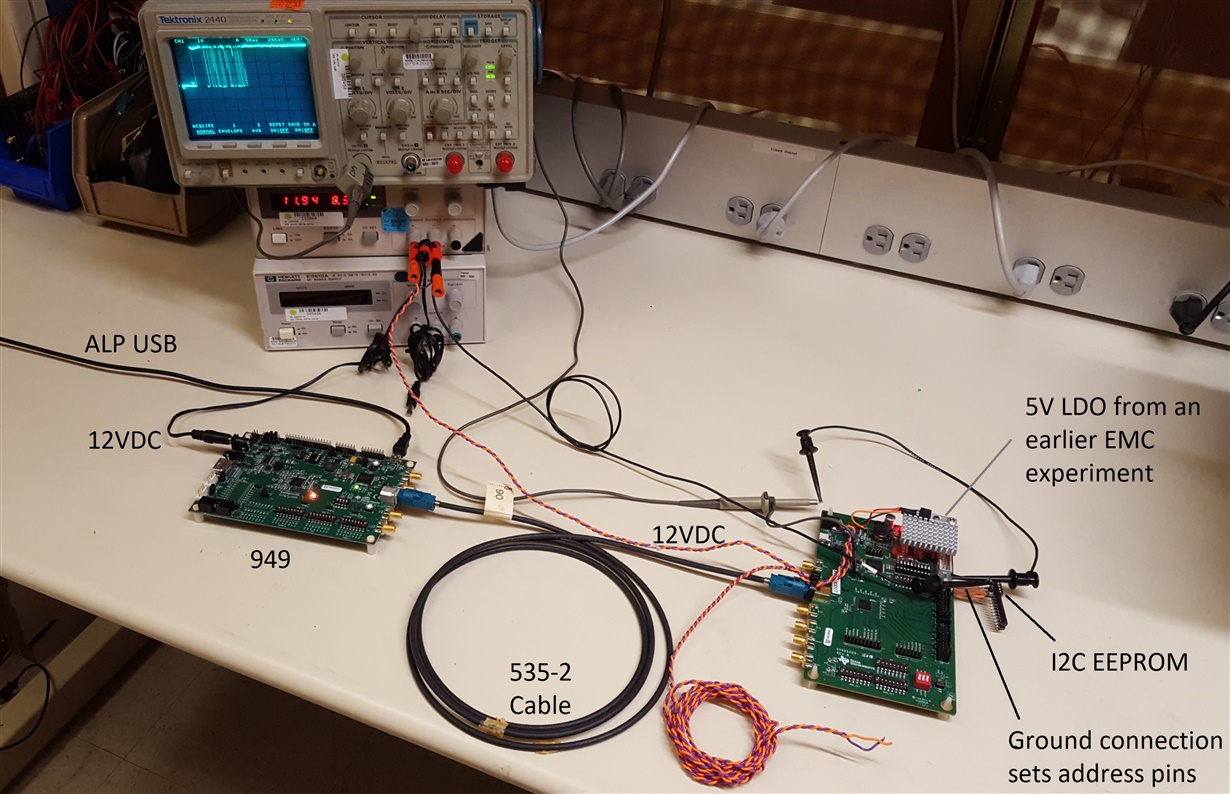

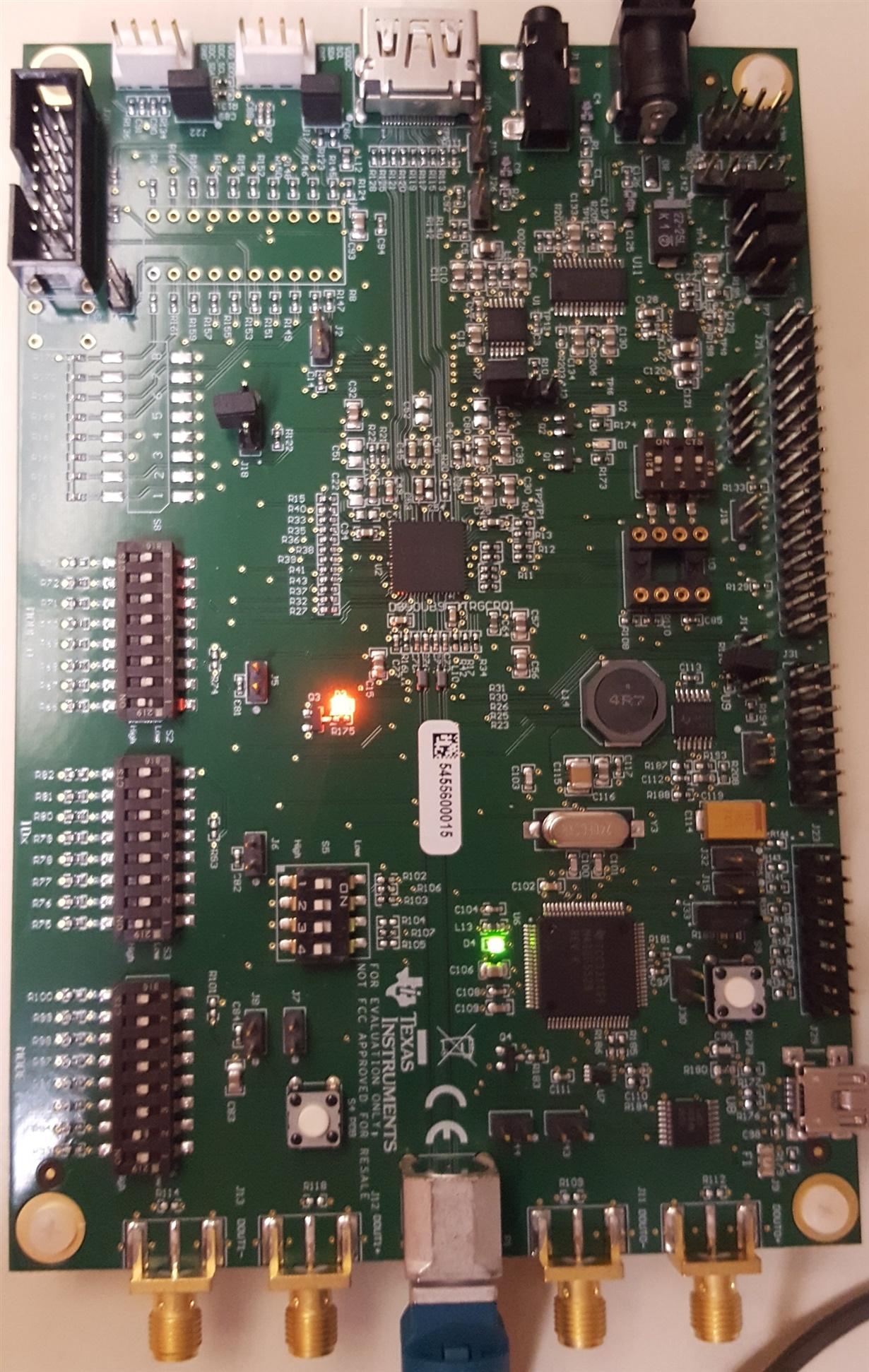

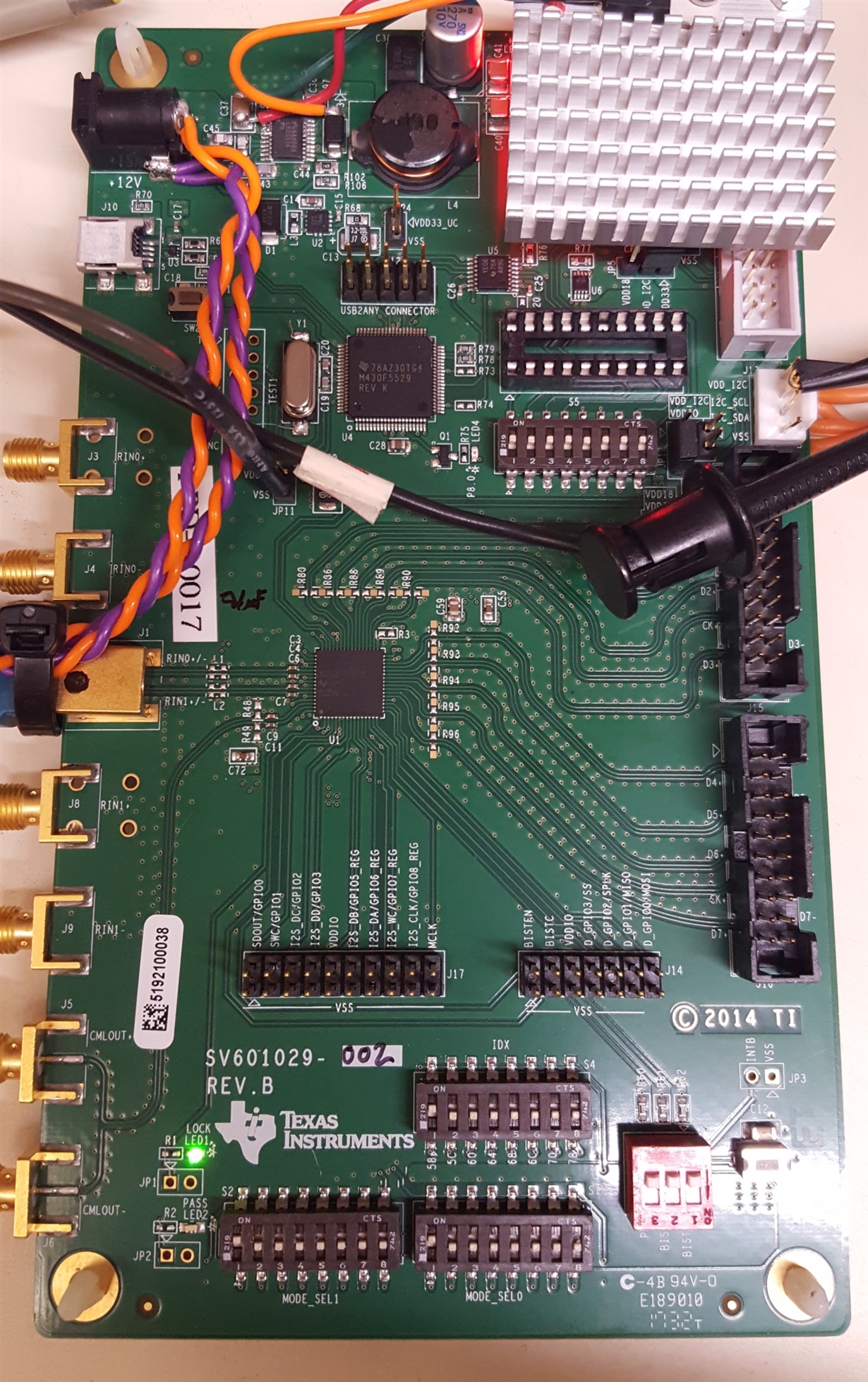

We are using serializer DS90UB949 evm and our deserializer to which EEPROM is connected with 0x50 (7 bit) address.

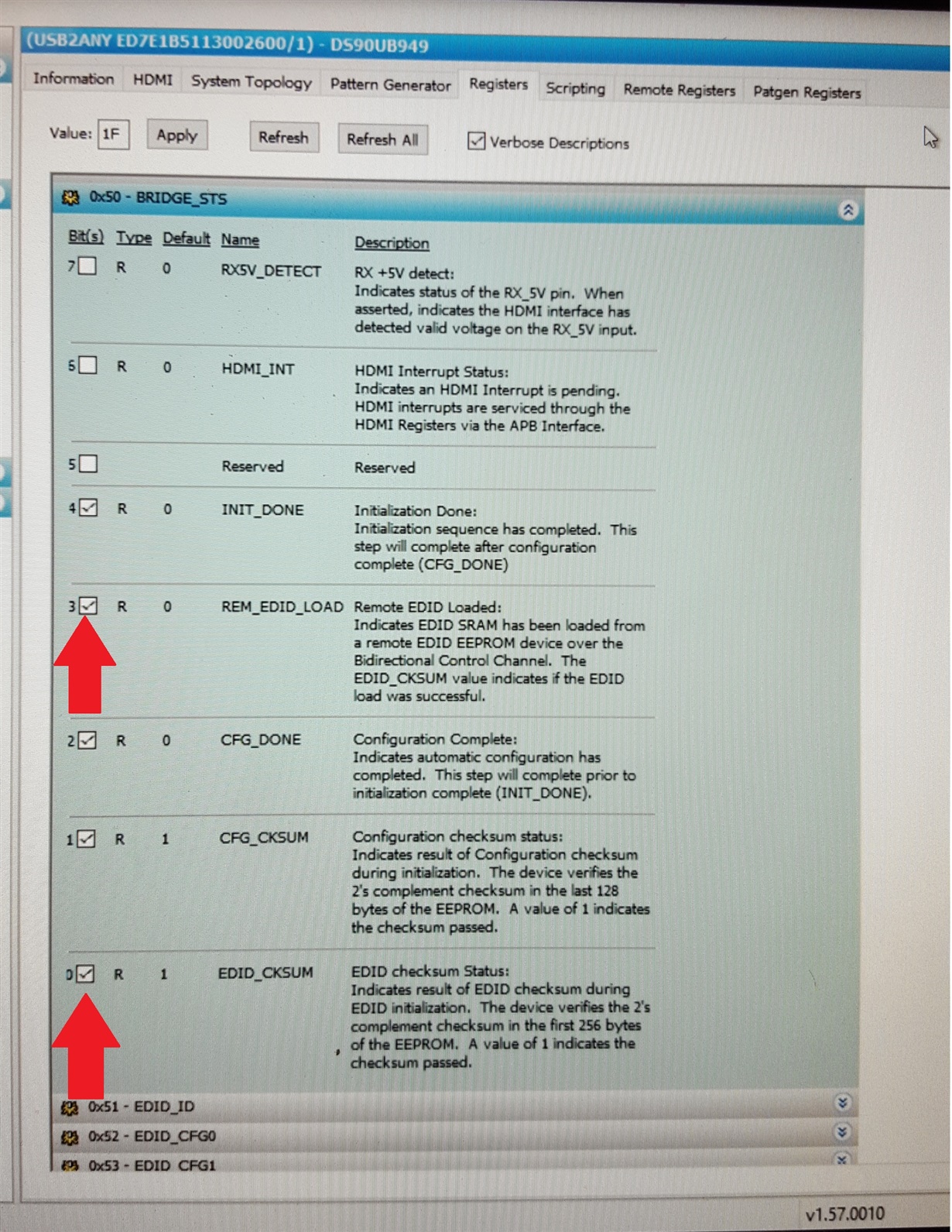

Issue: We want the EDID stored in EEPROM to be loaded to SRAM of serializer but we are able to see Internal pre-programmed EDID in the SRAM. This shows EDID stored in EEPROM is not loaded to SRAM.

Mode select configuration settings:

We are keeping MODE_SEL0 as 1 and MODE_SEL1 as 4 for External remote EDID configuration.

Below are the register dump of serializer(0x0c) and deserializer(0x2c),

=====================================================

msm8996:/data # ./i2cdump -f -y 8 0x0c

./i2cdump -f -y 8 0x0c

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 18 00 00 da 80 00 58 50 50 00 04 00 07 25 30 03 ?..??.XPP.?.?%0?

10: 00 00 00 a8 00 00 fe 1e 7f 7f 01 00 00 00 01 00 ...?..?????...?.

20: 0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a ?.%.....? ?..?Z

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 14 55 00 00 80 00 00 00 00 00 00 00 00 00 00 00 ?U..?...........

50: 97 a0 1e 00 28 0c 00 00 00 00 dd a0 02 06 44 48 ???.(?....????DH

60: 22 02 00 00 10 00 00 00 00 00 00 00 00 00 00 00 "?..?...........

70: 78 28 a0 00 00 00 00 78 28 a0 00 00 00 00 00 00 x(?....x(?......

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 a8 00 28 00 00 60 c0 00 00 00 00 00 ff 00 ..?.(..`?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 a8 00 28 38 00 00 00 00 00 00 00 00 00 00 ..?.(8..........

f0: 5f 55 42 39 34 39 00 00 00 00 00 00 00 00 00 00 _UB949..........

msm8996:/data #

msm8996:/data #

msm8996:/data # ./i2cdump -f -y 8 0x2c

./i2cdump -f -y 8 0x2c

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 58 04 00 f0 fe 1e 00 18 00 00 00 00 00 00 00 00 X?.???.?........

10: 00 00 00 00 00 00 00 00 00 01 00 00 0b 13 50 05 .........?..??P?

20: 00 00 40 28 08 00 83 84 01 00 00 00 00 00 00 00 ..@(?.???.......

30: 00 00 90 25 01 00 00 9e 00 00 00 01 20 e0 23 00 ..?%?..?...? ?#.

40: 43 03 03 00 60 88 00 00 0f 82 00 08 00 00 63 00 C??.`?..??.?..c.

50: 03 10 00 01 80 00 00 00 00 7f 20 20 00 00 00 00 ??.??....? ....

60: 00 00 00 00 10 00 00 00 00 00 00 00 00 00 00 00 ....?...........

70: 00 00 00 07 07 08 00 00 00 00 00 5d 02 00 00 00 ...???.....]?...

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 8c 00 00 00 00 00 00 00 00 00 00 00 00 00 ..?.............

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 00 00 00 00 00 00 c0 00 00 00 00 00 00 00 ........?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

f0: 5f 55 42 39 34 38 00 00 00 00 00 00 00 00 00 00 _UB948..........

msm8996:/data #

=========================================================

Below is the 0x4f register settings of serializer taken from the datasheet,

From this we can see 0x4f[0] is Read only and all other are RW bits, but we could able to write to 0x4f[0][3][4] bits and could not write to 0x4f[1][2] bits.

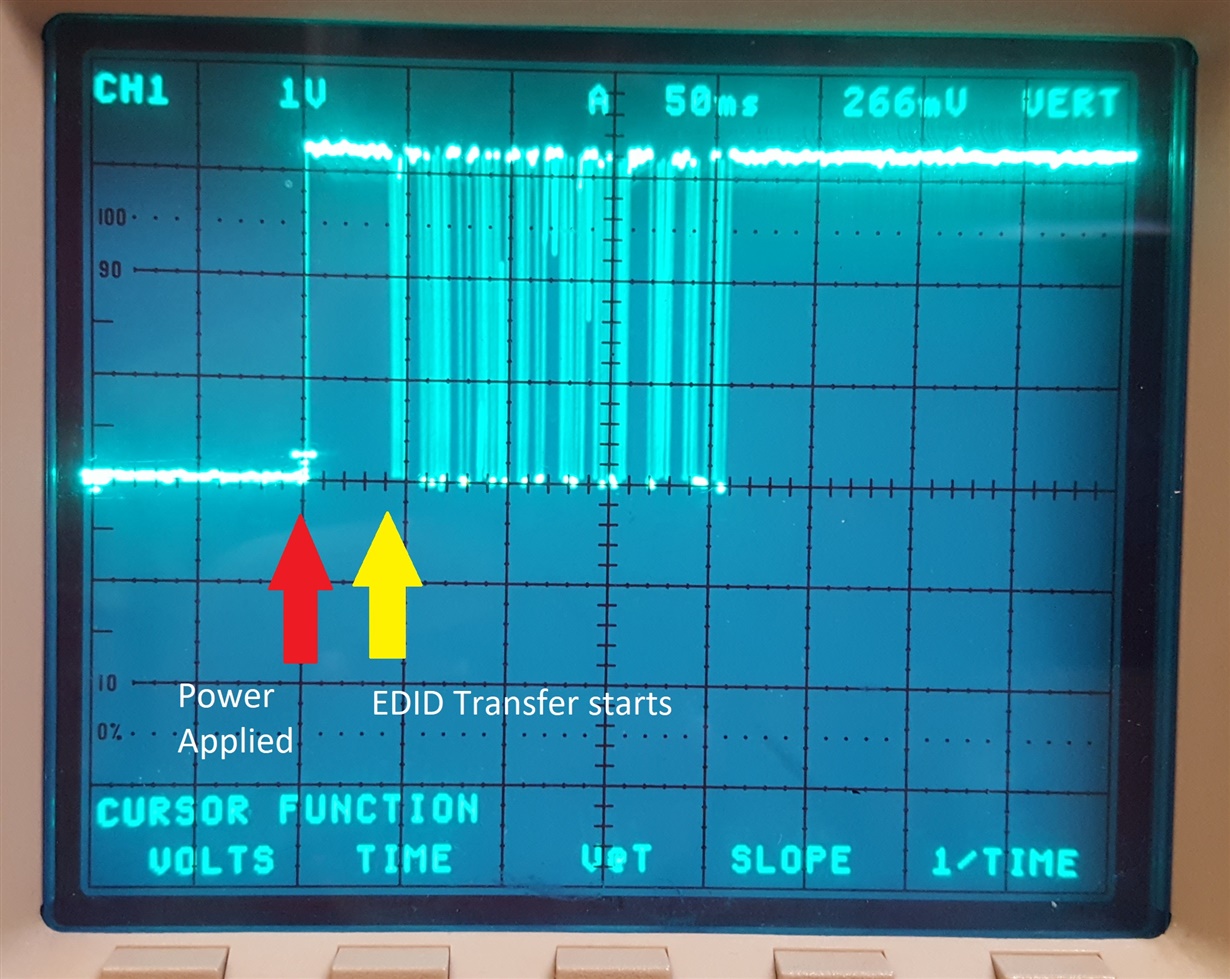

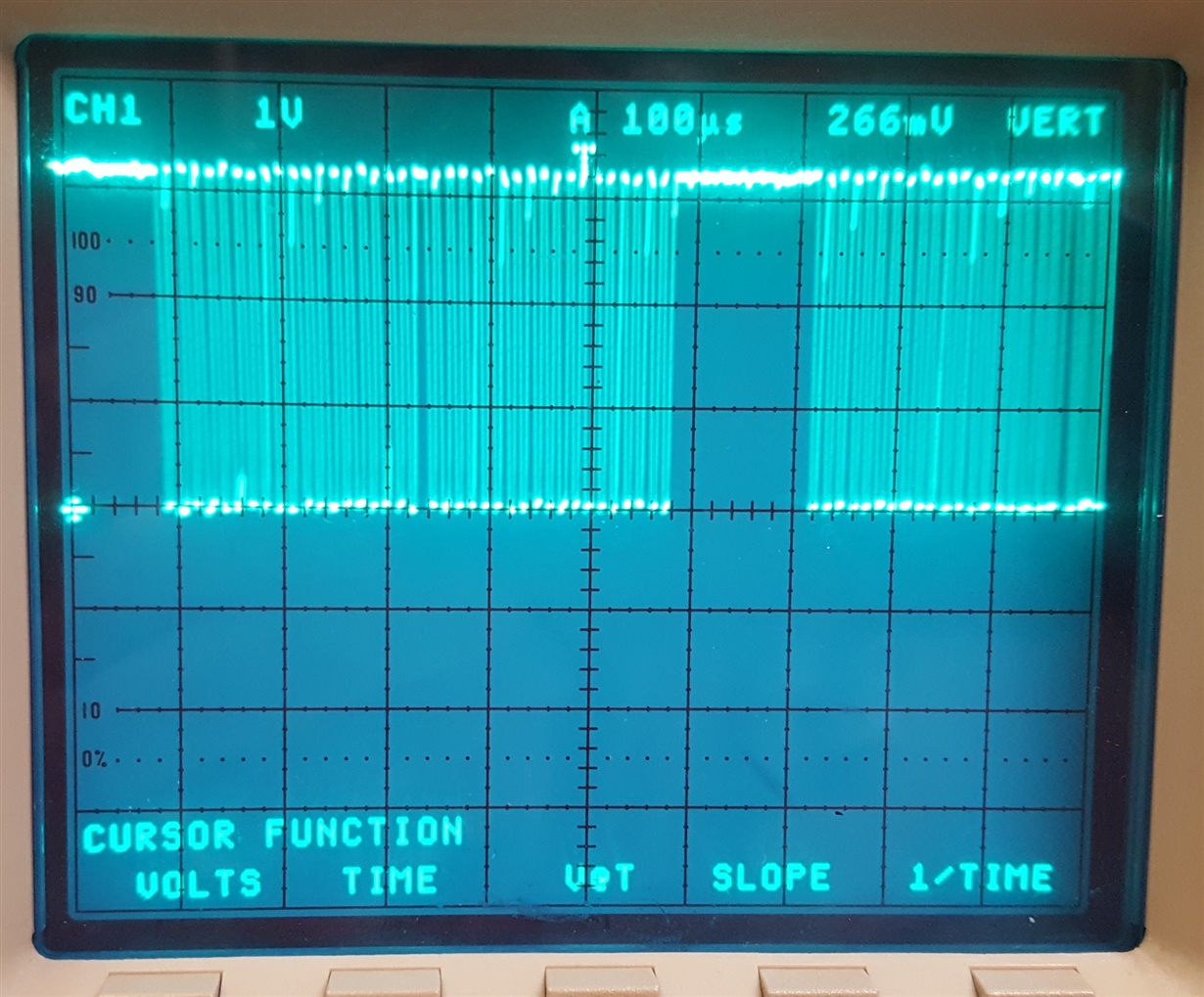

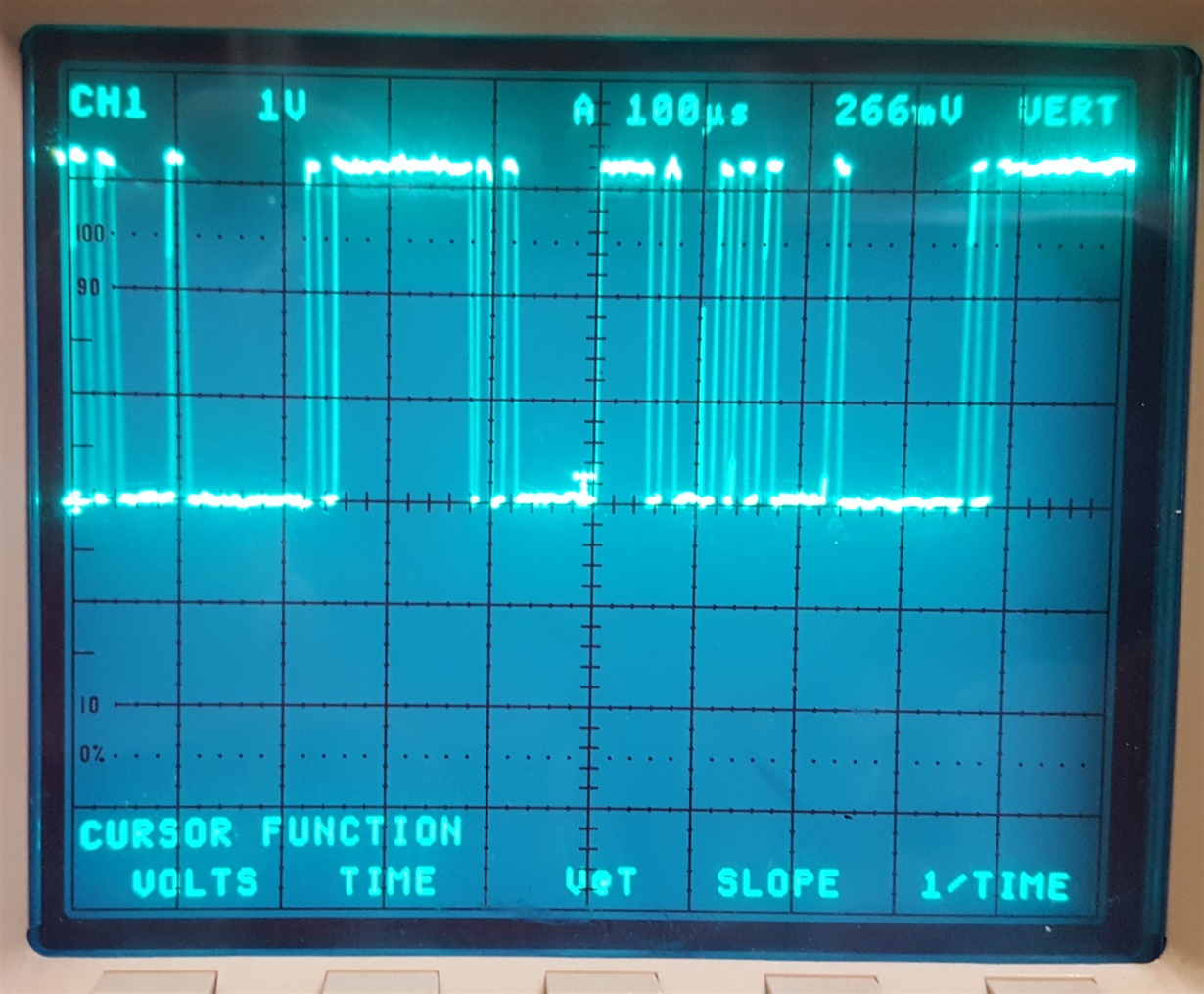

We have done some other experiments as well to make sure other EDID configuration supported are working fine. Below are the experiment results,

Exp1: Connecting EEPROM to DDC I2C:

1. External local EDID (EEPROM): We are able to read the EDID stored in EEPROM from the “/sys/devices/virtual/graphics/fb1/edid_raw_data” node, in the hex format.

2. Internal EDID (SRAM): We are able to read the EDID stored in EEPROM from the “/sys/devices/virtual/graphics/fb1/edid_raw_data” and “/sys/devices/virtual/graphics/fb1/edid” nodes, in the ascii format.

In both the cases we are able to read some portion of the EDID, not the complete 256 bytes what we wrote on EEPROM.

Exp2: Connecting EEPROM to I2C (BLSP_8):

1. External local EDID (EEPROM): We are not able to read any edid from the “edid” or “edid_raw_data” nodes.

2. Internal EDID (SRAM): We are able to read the Internal Pre-programmed EDID in this case.

Could you please us debug this issue?