Other Parts Discussed in Thread: DSI-TUNER

Dear team,

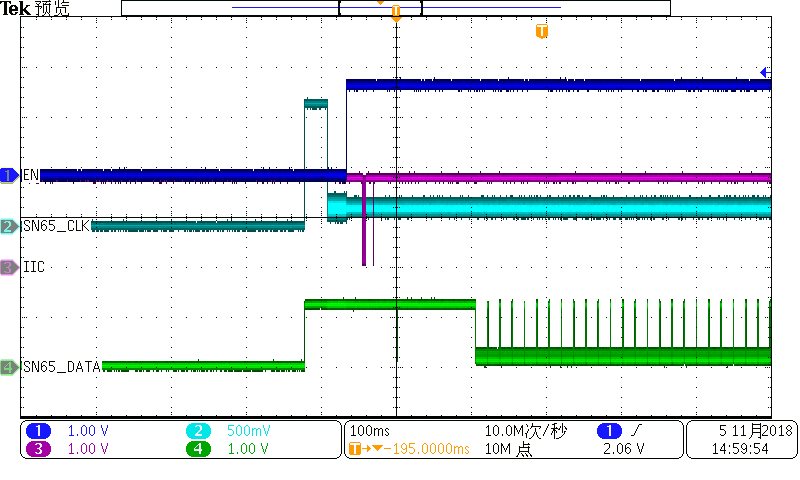

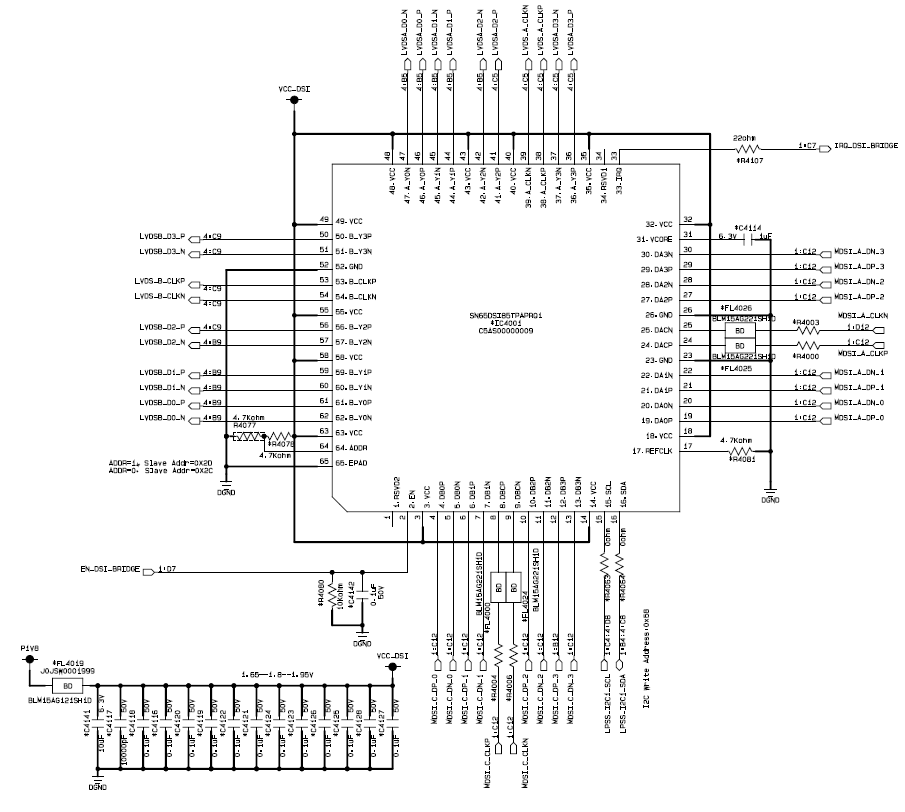

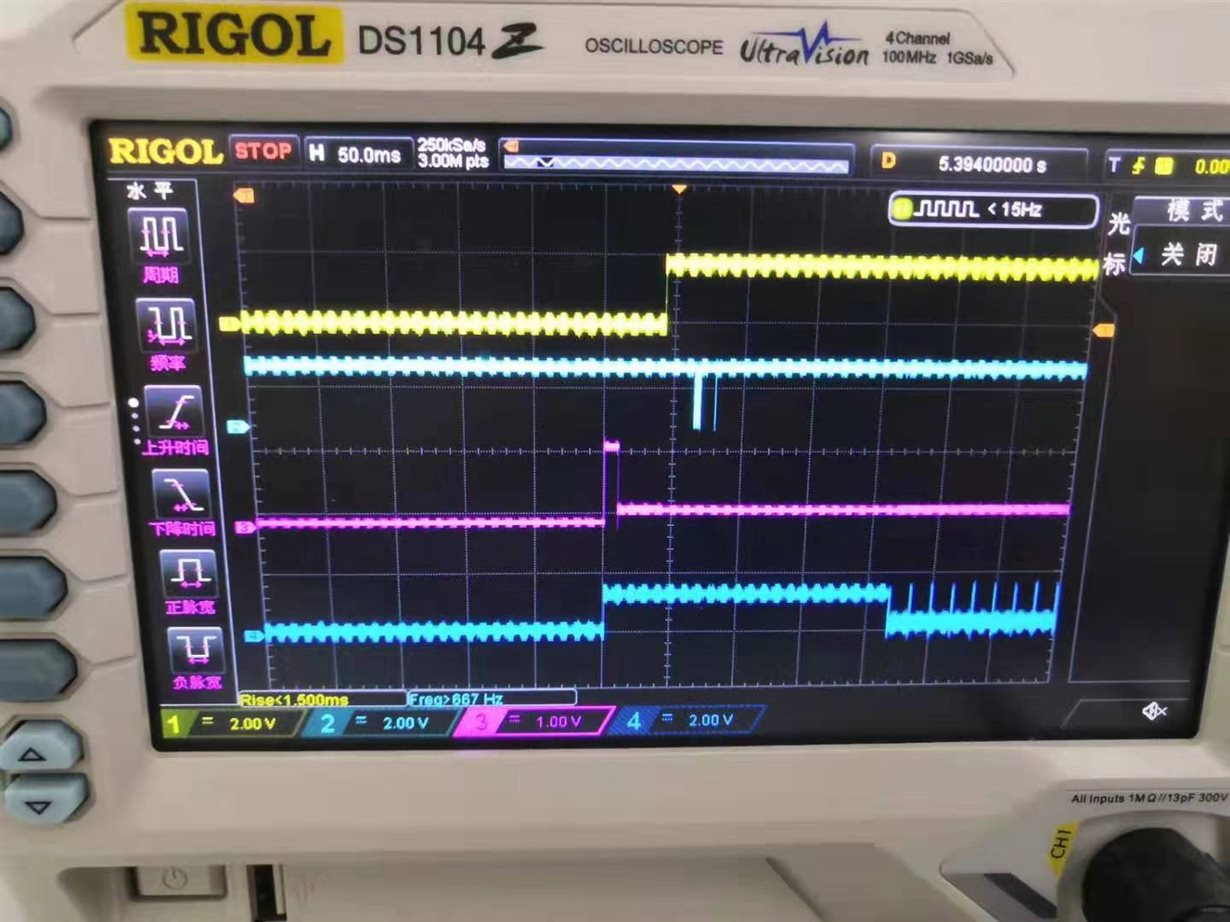

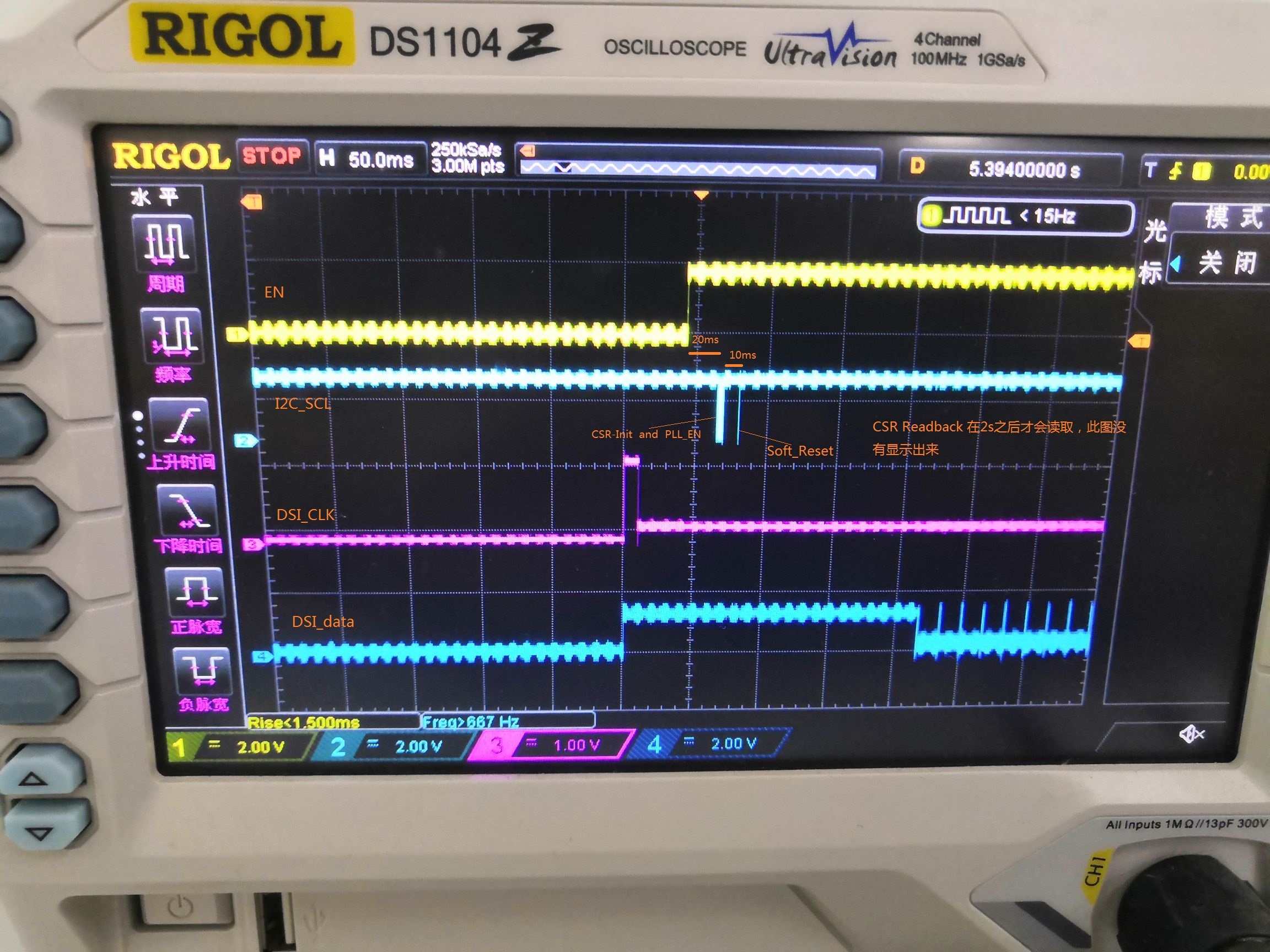

The oscilloscope measurement is used to find that the DSI85 input signal is normal, but one of the output terminals has no video signal output while has the backlight.

At this time, read CSR 0xE5 and CSR 0xE6, their value are all 0x00 which means no error detected.

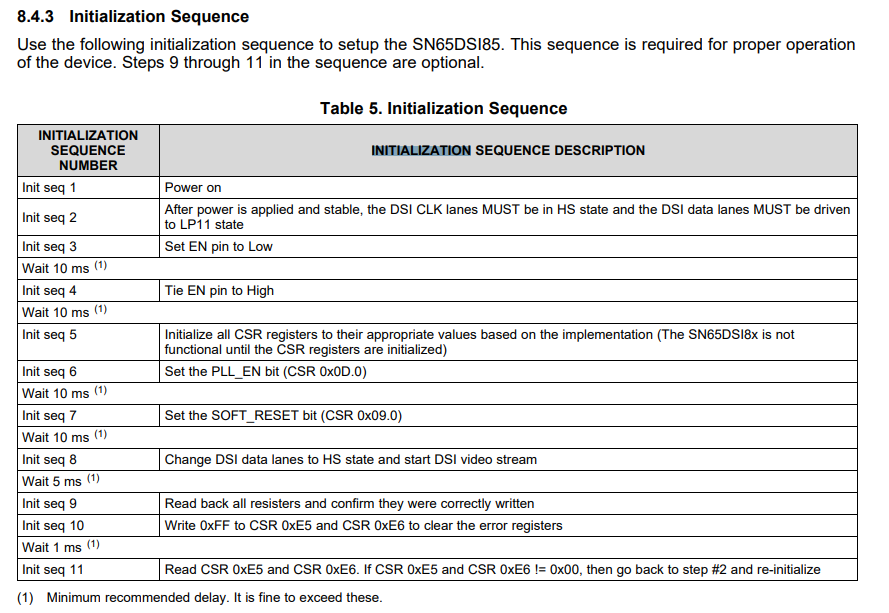

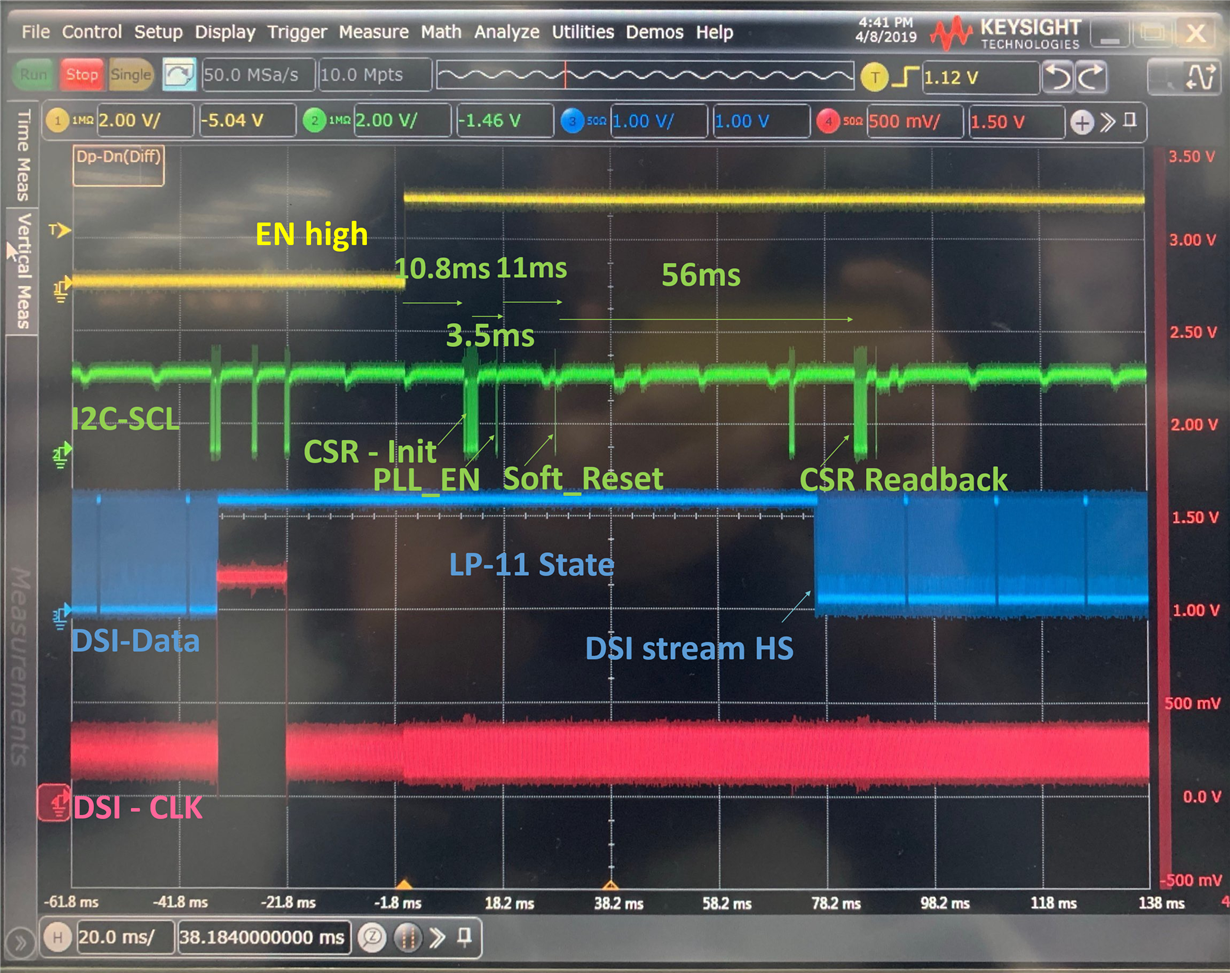

In addition, the power on sequence is as below, is there any problem about it?

Thanks & Best Regards,

Sherry