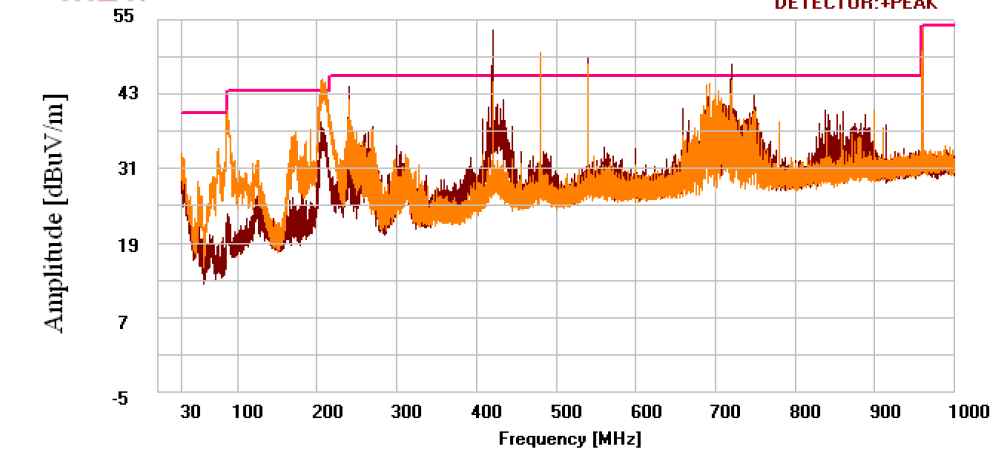

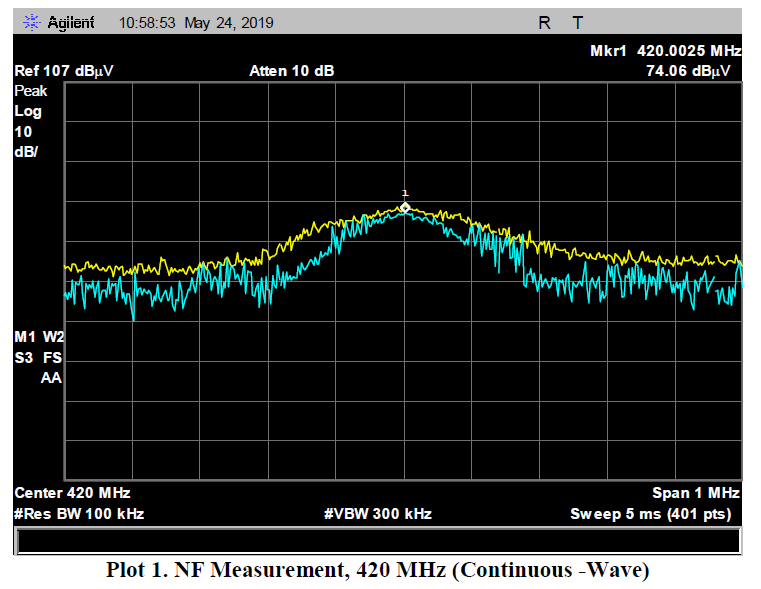

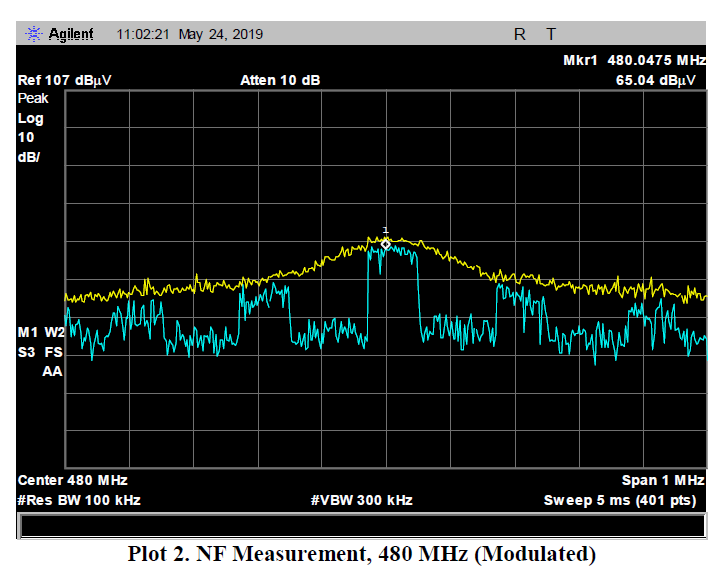

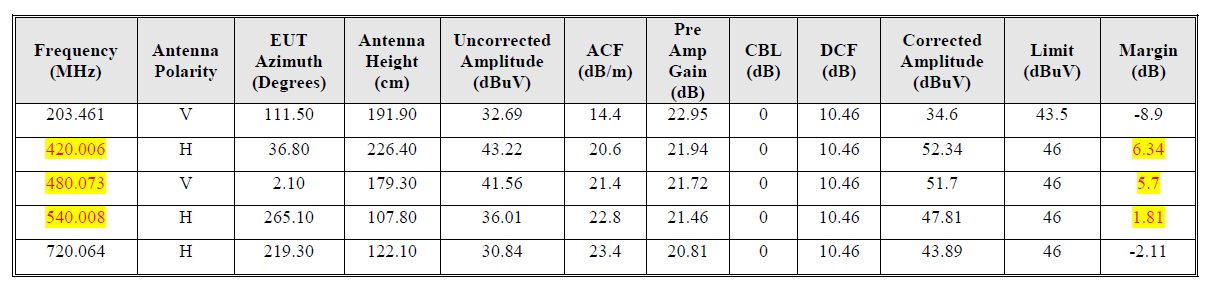

I have very little control over the TUSB1210 USB PHY in terms of EMI/EMC. I am using a Xilinx ZYNQ device to communicate over ULPI running at 60 MHz. My customer is testing our board in their setup. They failed FCC Rule 15. I am asking the customer to just test Full Speed instead of High Speed to see if the problem areas move around relative to the USB data rate. Since I have very little control at this device level, I am looking for options that might help reduce the EMI/EMC. I didn't see any slew rate items in the memory map. I see in the datasheet in Section 4.1 (Datasheet revised August 2012) that the USB PLL generates both the 60 MHz ULPI and the USB data interface rate (480 Mbps). I use a 24 MHz clock from the FPGA to feed the TUSB1210.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.