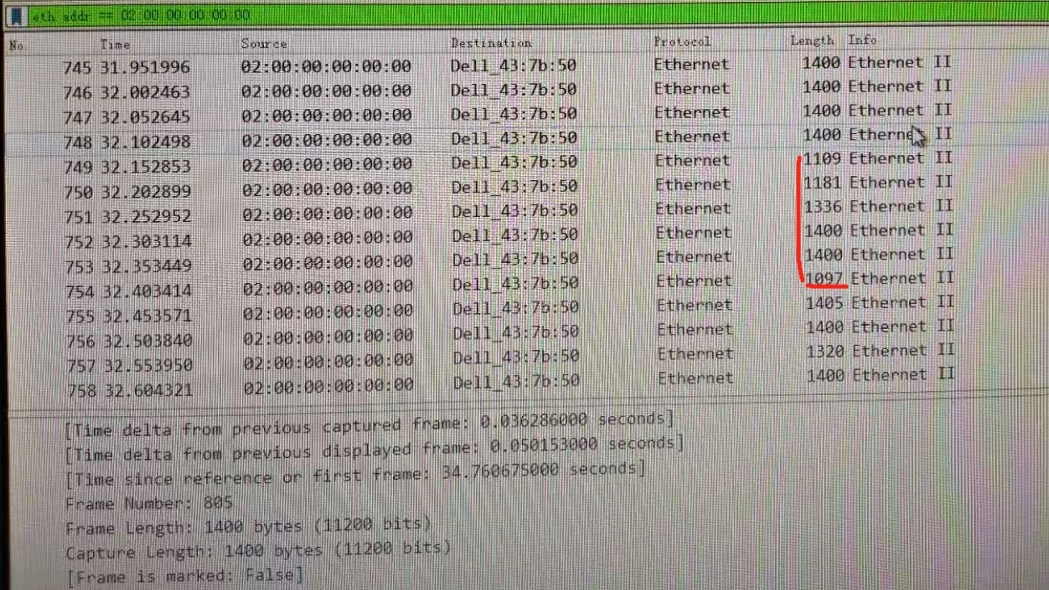

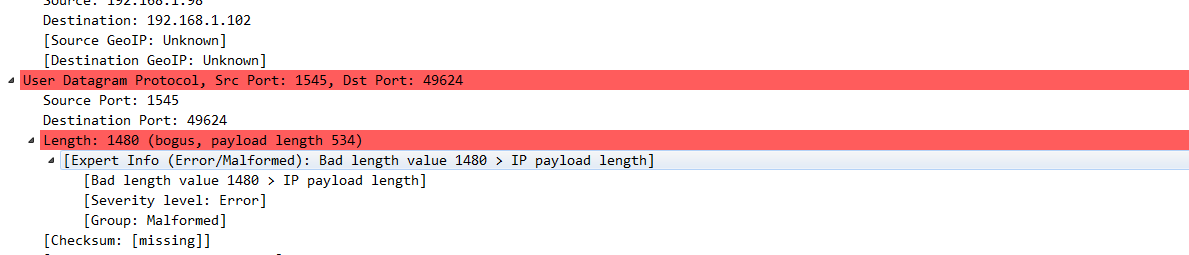

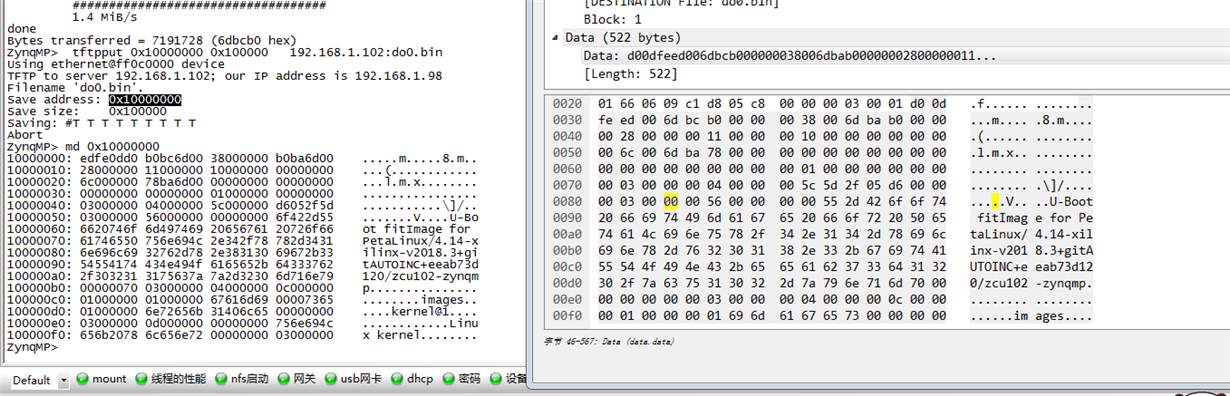

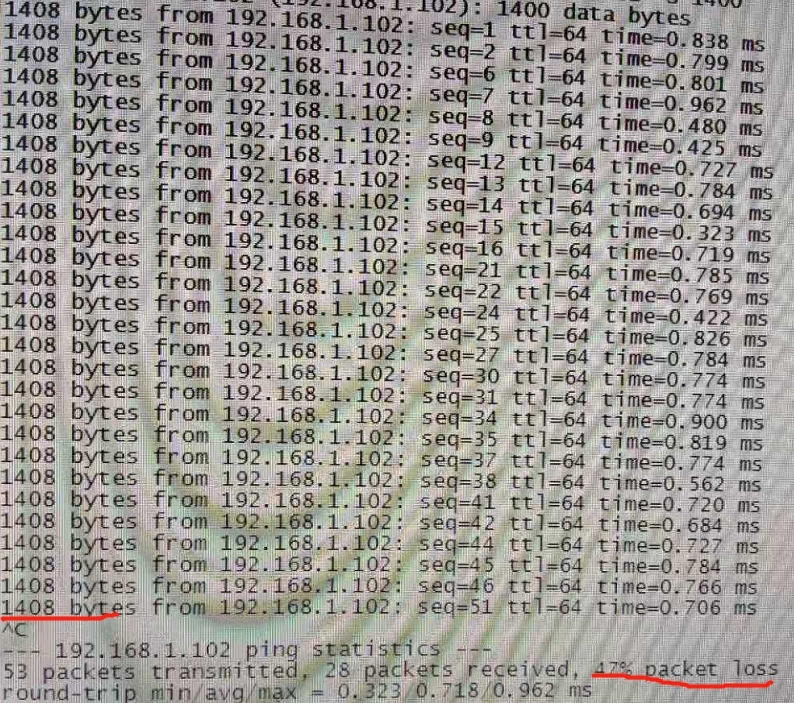

My design is using a DP83867 connected to a Xilinx Zynq running Linux. When connect 1000Mb-T,The receiver works great,but the transmitter can‘t work in high speed, only can reach kb speed . When connect 100Mb-TX,the receiver and transmitter can’t work great ,only can reach kb speed .

I can ping other addresses correctly.

I've noticed in the ISR register 0x0013 that bit 2 XGMII_ERR_INT is set 1 witch is diffrent from demo.

someone say the problem maybe the 25Mhz clock or 33.33Mhz clock,I confirm the two points,they are ok;

besides,how can i change the register value trough the net on linux systerm?

Does anyone know what cause the problem?thankyou