Other Parts Discussed in Thread: DS90UB962-Q1, , DS90UB933-Q1

Hi Sir,

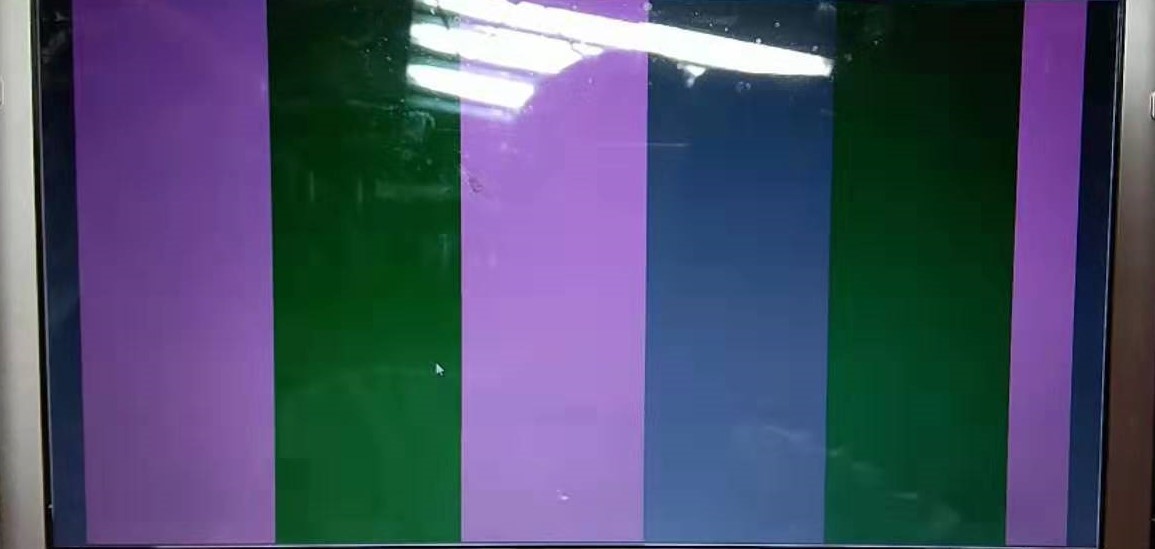

Need help to review the setting. There has issue in DS90UB953 connect to DS90UB962.

Current information as below:

DS90UB962 i2c id: 0x60 (8bit)

Use “RX0” Channel

DS90UB962 CSI_output use 0

962 to 953 setting as below:

0x6D=0x78

0x10=0x00

0x4C=0x01

0x58=0x5E

0x32=0x01

0x33=0x01

DS90UB953 is using yuv 8bit mipi 4Lane CMOS sensor

DS90UB953 I2C ID is 0x32(8bit)

Need 962 to 953 mipi 4Lane YUV “initial table”

Kindly help to provide suggestion, thanks.

Ja