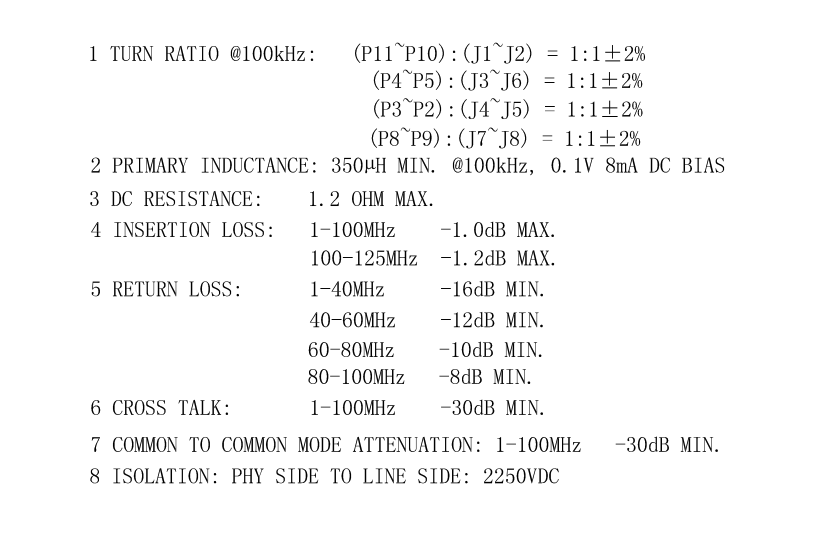

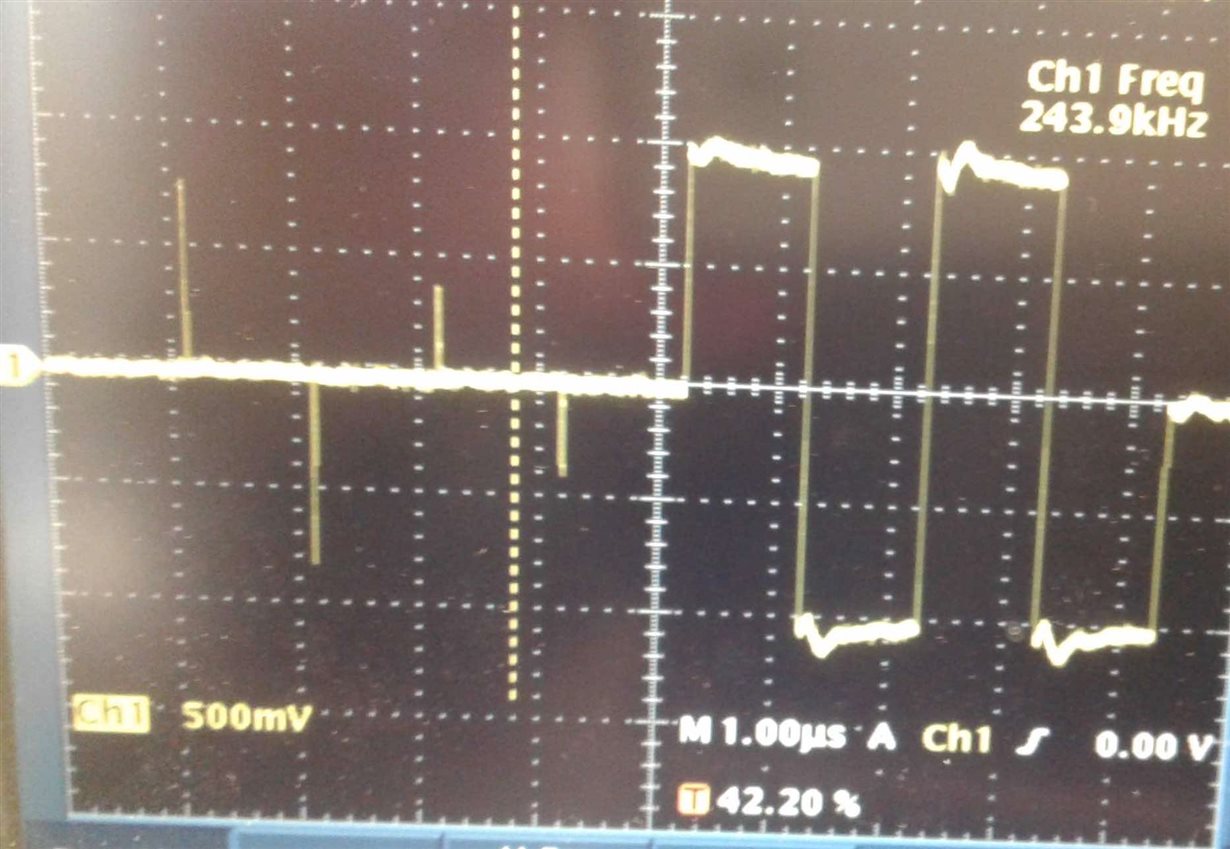

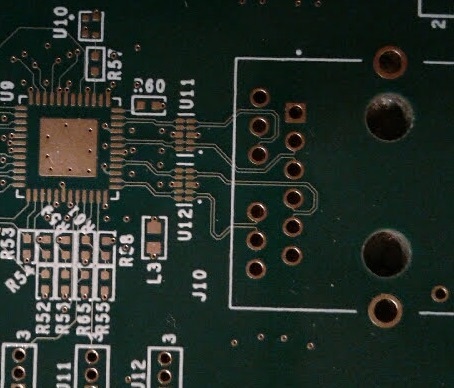

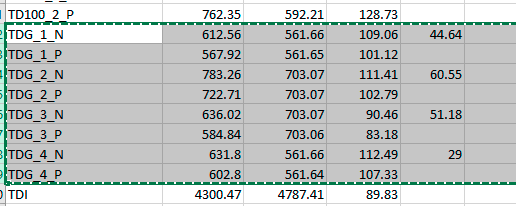

We have a board using the DP83867IRRGZT part. We have a problem with CRC errors on the link. It seems that the analog side is the problem. With reverse loopback enabled, we get about 5% packet loss, and the computer interface says they are due to CRC errors. We are using the TE integrated magnetics 6-2301994-1, which from what I can see meets all the requirements for the magnetics. We designed the board with 100 ohm differential impedance, and we use TPD4E05U06DQAR TVS components on the data lines on the PHY side of the magnetics.

The link comes up and works normally apart from the packet loss. I have gone through the troubleshooting guide, and I don't see anything in there that is a problem.

I would appreciate any ideas for getting this fixed.

Thanks!