Hello,

I have a question on the High-Speed SERDES in TLK10002.

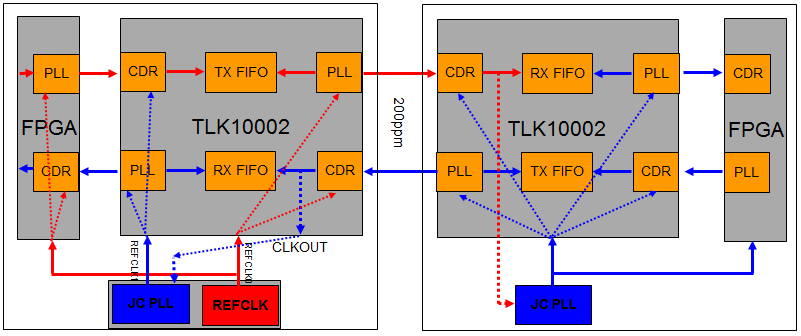

Does HS SERDES have master mode and slave mode? I want to make clear which clock the Transmitter of HS SERDES uses. According to the datasheet, HS SERDES can internally provide two clocks:

1. the clock synchronized to the external reference clock - VCO_CLOCK_x_DIV2

2. the clock recovered from the incoming serial data - HS_RXBCLK_x

Will the transmitter of HS SERDES always choose its clock temporal synchronized to the external reference? Or will it choose the clock according to the working mode? For example, it selects the clock synchronized to the external reference clock in master mode. However, it selects the clock recovered from the incoming serial data in slave mode.

Best regards,

Peter

Regards,

Regards,