Hi,

we are using the sn65lvds348 quad receiver as an LVDS to LVTTL interface.

The EN control pin is pulled up to 4k7. All the output pins (LVTTL side) are pulled down to GND through 4K7 to ensure a known stat when EN/ is inactive.

EN/ is controlled by a remote processor.

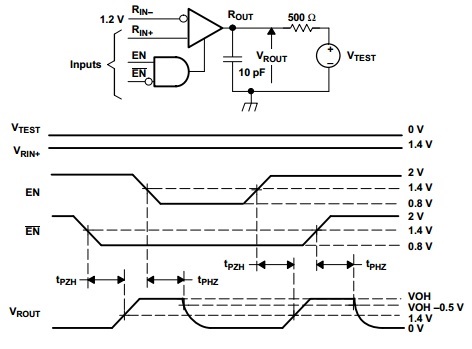

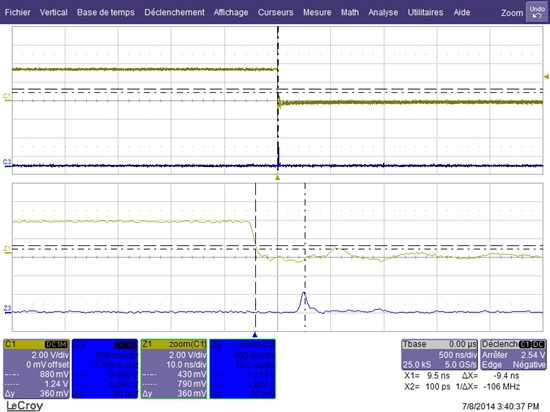

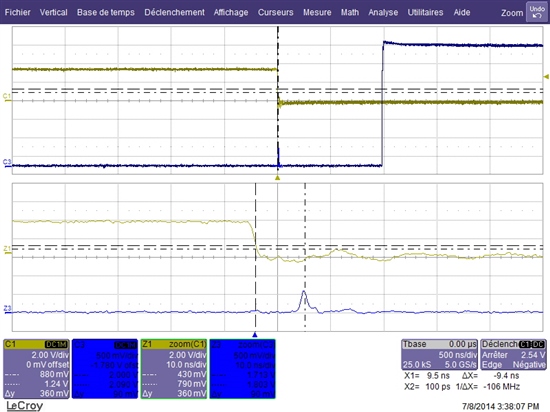

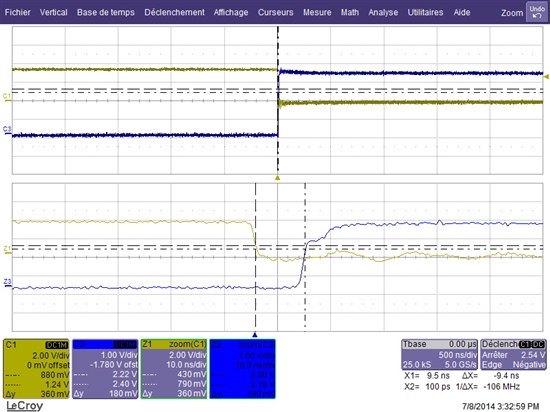

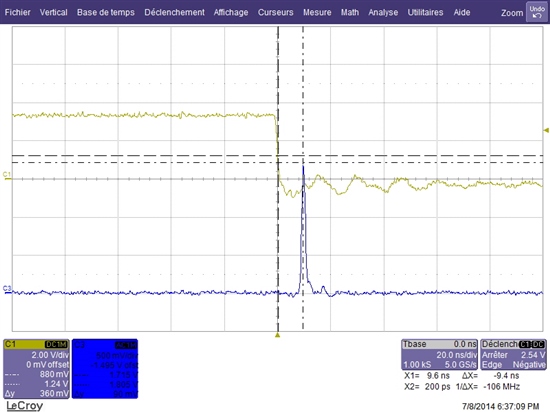

We noticed the following: when the differential inputs are biased such that the output should be a logic zero and the EN/ control input toggles from high to low, a glitch appears at the output 9 ns after EN/ was asserted low.

The glitch size grows when the temperature drops: a glitch of less than 500 mV at ambient becomes higher than 2V at -40 °C.

Is this a known issue? Is there a workaround?

Thank your for your help.