Hello,

We have designed an LMH0031 on to a card and with a good quality SDi signal applied to the inputs there is no data output and no VCLK. The circuit is wired to use the internal 27MHz oscillator, which has been enabled and is working correctly. After reset the ACLK pin is toggled three times, as required by the datasheet. Also, tried using the internal test pattern, colour bars, but still no VCLK.

The +3V3 is used to power a +2V5 LDO, so +3V3 should be available before the core +2V5 is applied.

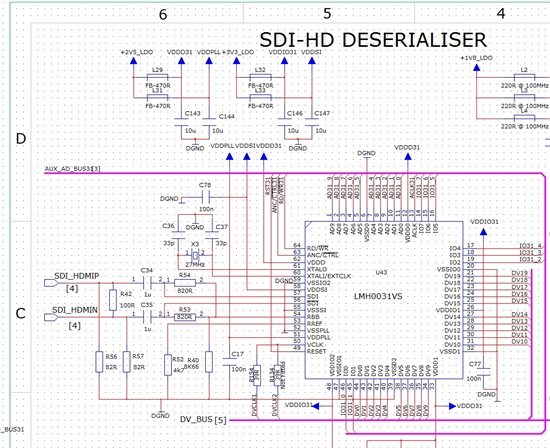

Attached is the schematic of the LMH0031. Please note the schematic symbol has been drawn in a mirrored format, but the PCB footprint is correct.