Hi Team,

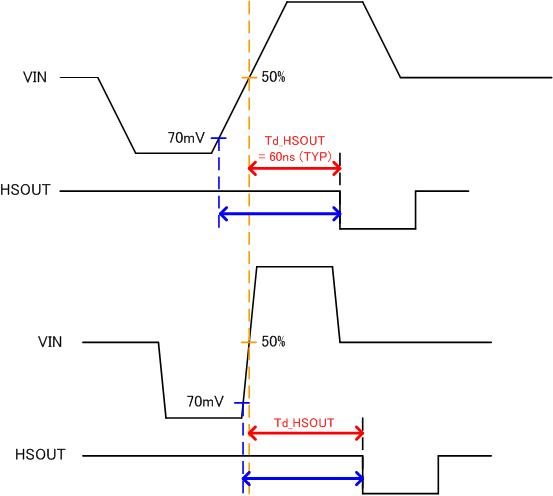

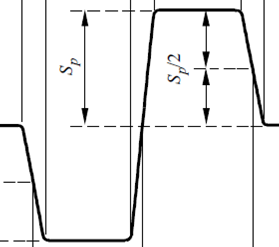

The rise time of tri-level sync signal for 1080i is normally f=0.054us. The datasheet defines t_HSOUT as 525ns(TYP).

However, our customer would have a tri-level sync signal with very steep rise time f=0.00675us.

Could you advise us how t_HSOUT timing would change in this case ? They require HSOUT timing information for this condition.

Thanks in advance.

Best Regards,

Kawai