Hi all,

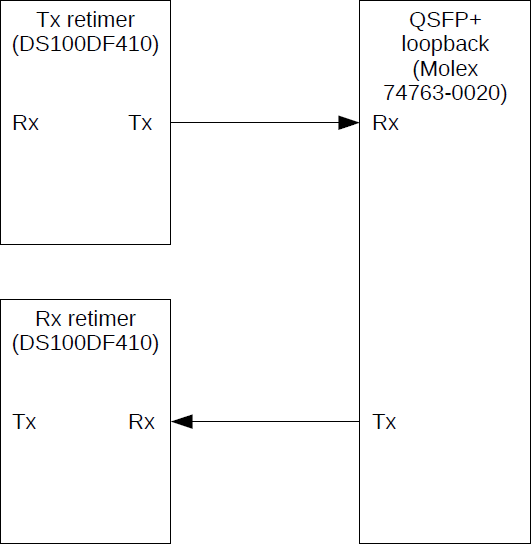

Currently we are trying to tune DS100DF410 retimers. We are using the internal PRBS pattern generators and Eye Opening Monitors. Using a QSFP loopback module we are sending the bit patterns from retimer 1 to retimer 2. It is very hard to tune the retimers since many settings can be changed. Is there a sort of tuning procedure available?

Thanks.