Dear, Sir.

My customer is applying DS90UB913A-Q1 with external OSC for CIS.

And they are used under 10 bit mode.

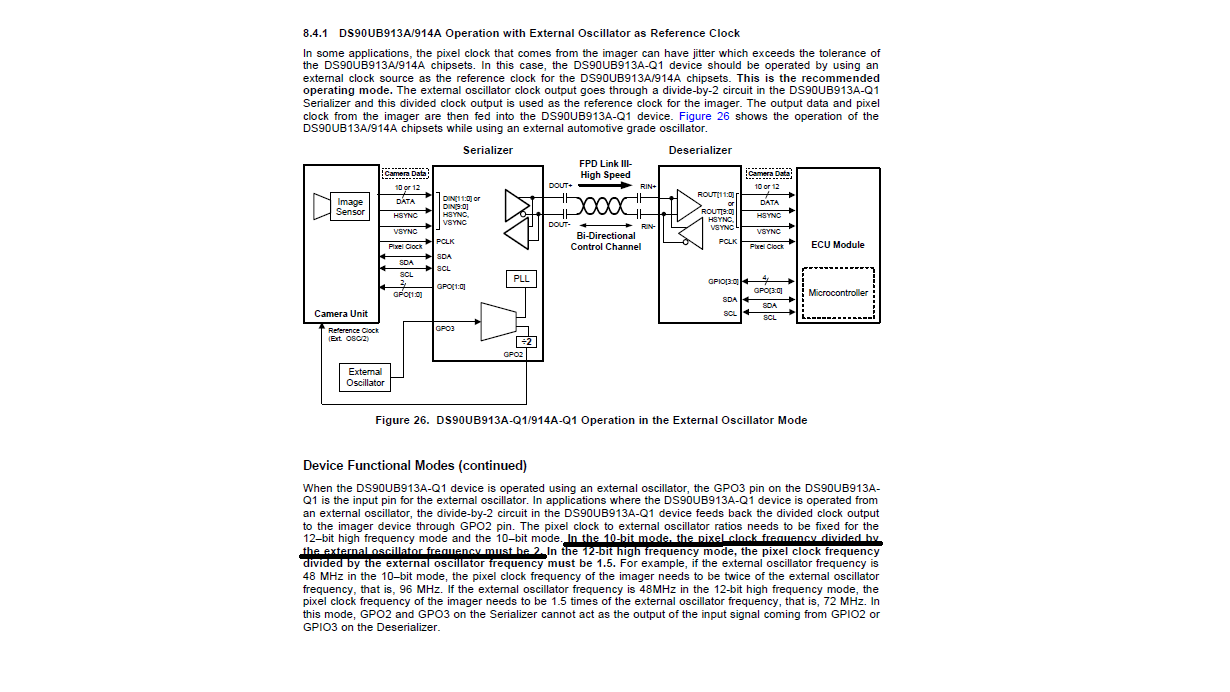

Datasheet, Figure26 shows divided -by-2 block on the output for CIS.

However, following expains "pixel clock frequency divided by external

OSC frequency must be 2".

I think it looks having a constradiction. I would like to make sure which is correct.

Please give your advice.

Best Regards,

H. Sakai

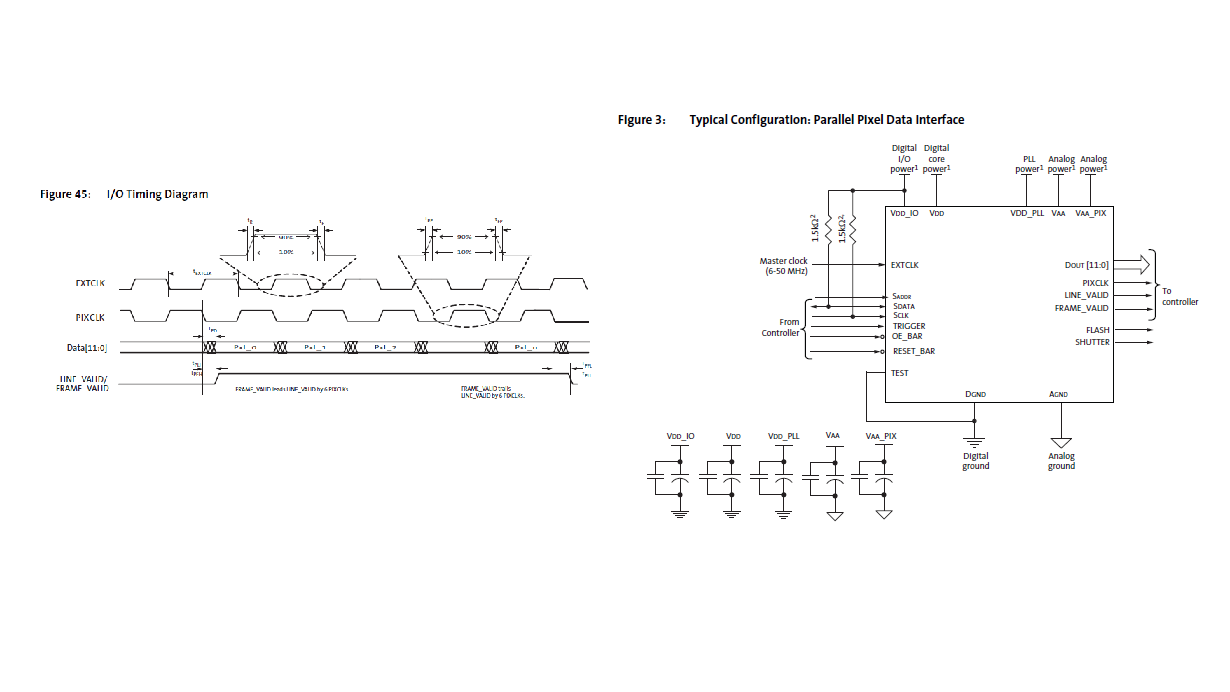

I have checked normal 1Mpixel/10bit parallel output CIS datasheet. Input CLK for CIS is directly reused as PCLK.

If the external OSC=54MHz, CIS input CLK=27MHz, PCLK=27MHz.

PCLK/external OSC = 1/2.

We need your advice it is no problem for DS90UB913A-Q1.

H. Sakai