Dear Sir,

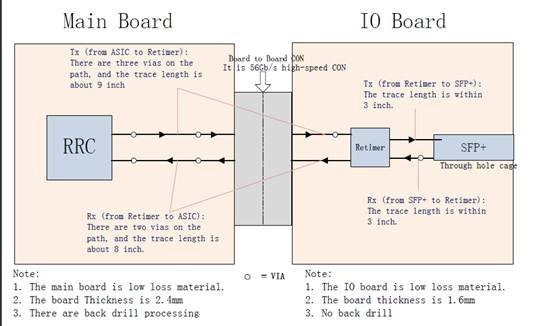

I have a project which uses the SFI Retimer DS100DF410 to output 16x SFP+ Port. But, with the initial retimer configuration, the SI test result of the 16x SFP+ Ports are all failed. The fail phenomenon are descripled as blow:

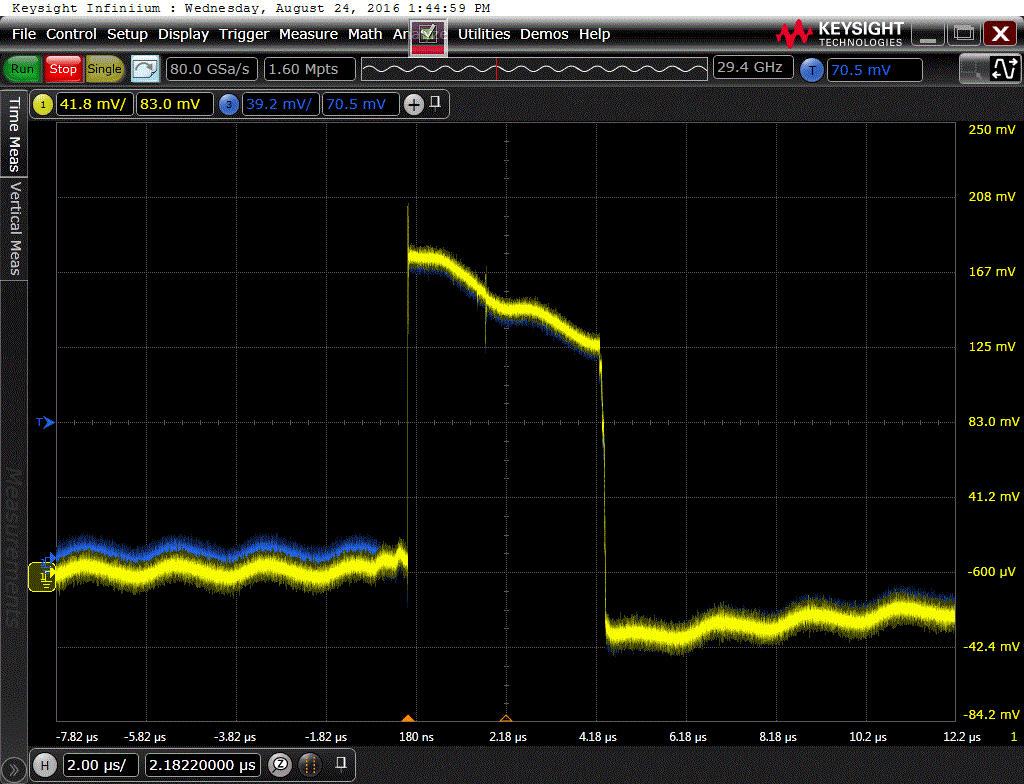

A. The 8180 Pattern is wrong.

B. The PRBS9 Pattern is fail.

C. Just PRBS31 Pattern is pass.

So, Is this SI fail caused by the initial retimer configuration ? If yes, why the 8180 pattern is wrong ? Thank you very much !