Hello Team,

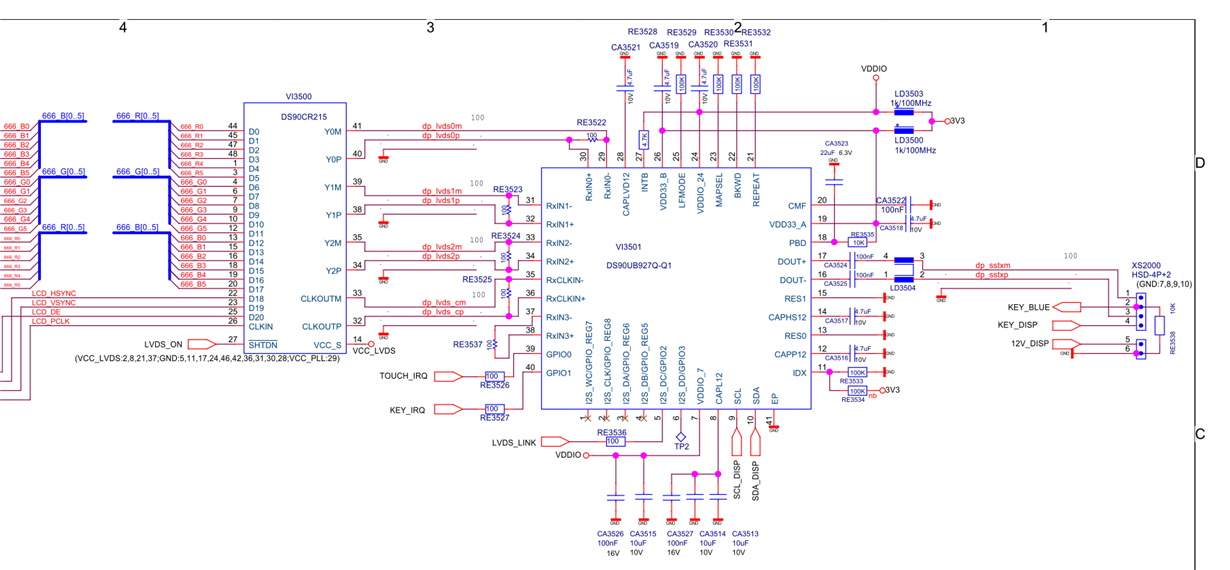

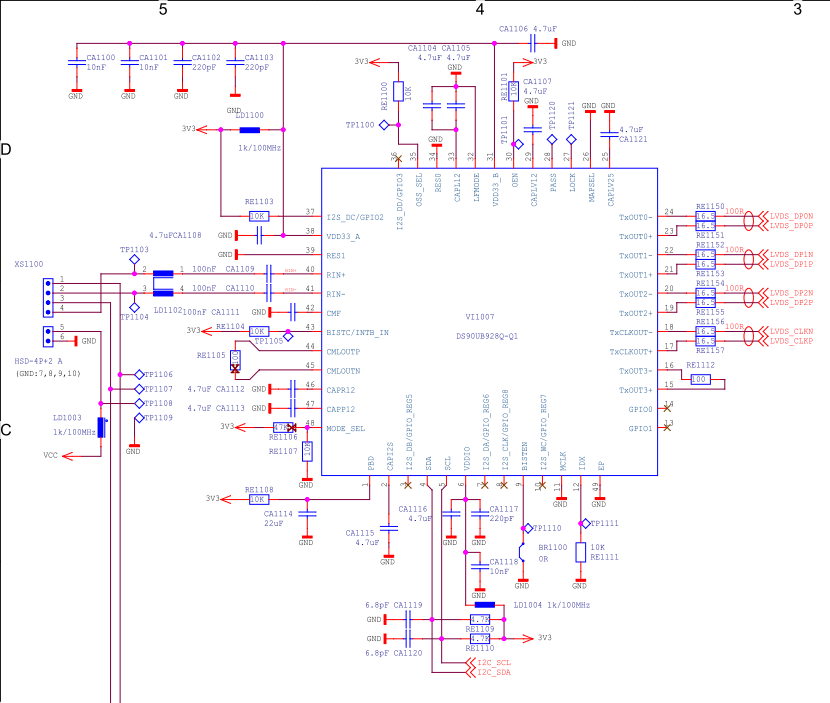

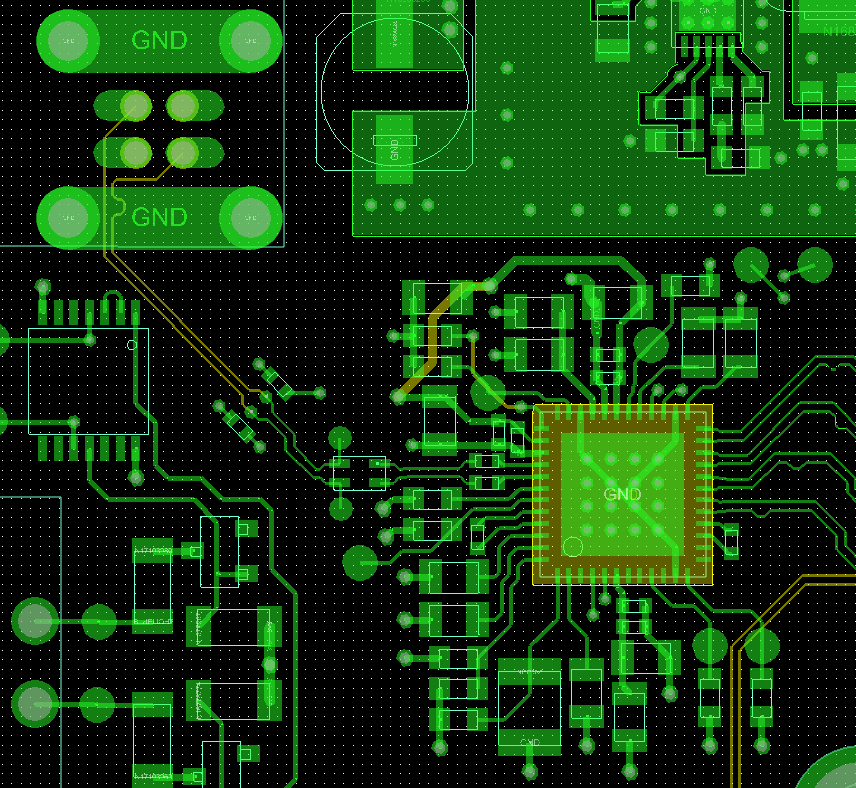

My customer uses the DS90UB927/DS90UB928 pair to transfer FPD Link III data at a pixel clock of 74MHz. Datasheet mentions 85MHz pixelclock support, but they only get a stable link with upto 42.5MHz clock. The Fig 12 in the datasheet shows typical characteristics with 78MHz clock. As 42.5MHz is exactly half of 85MHz I thought if there was any misinterpretation on the measurements.

Test results:

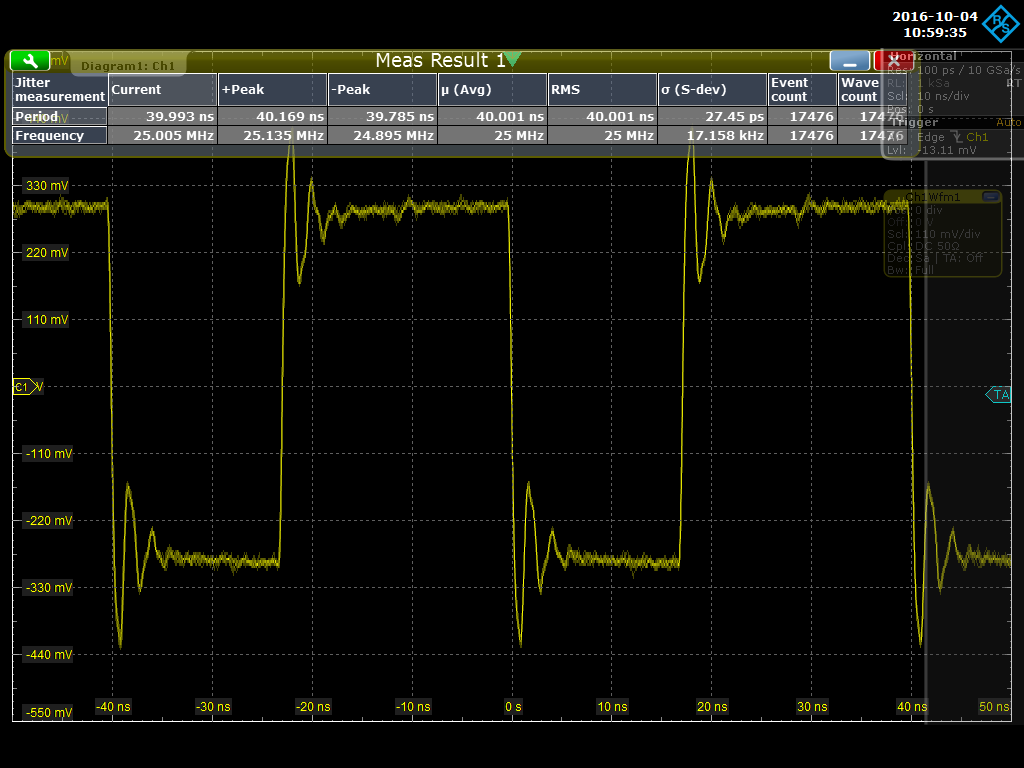

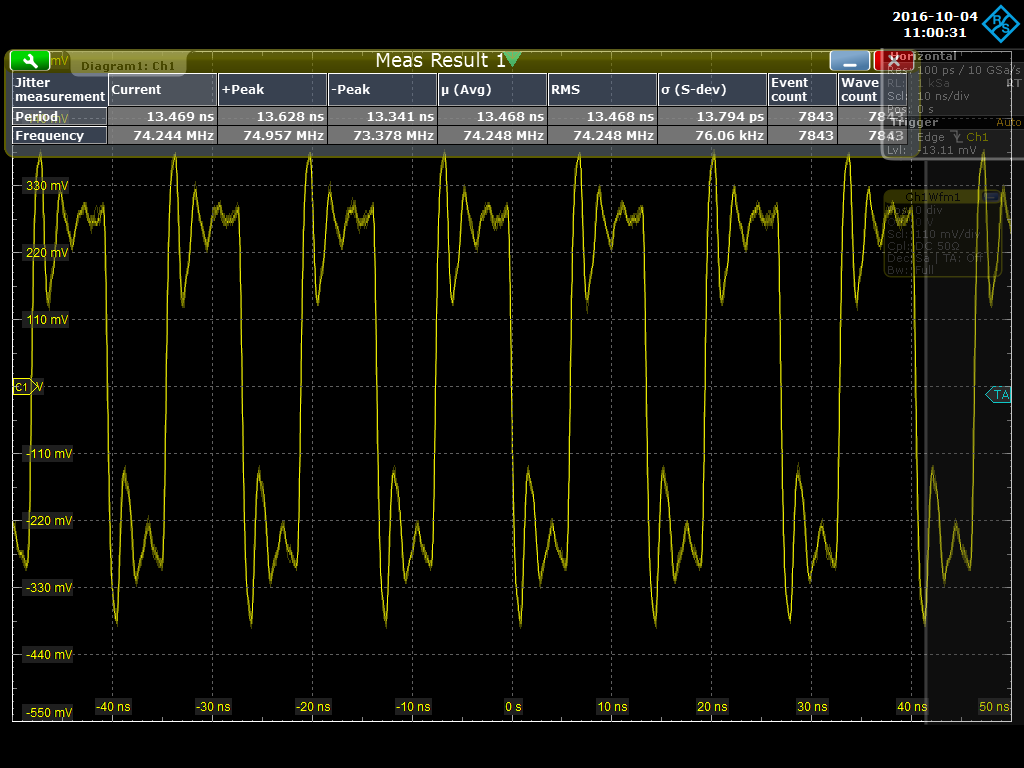

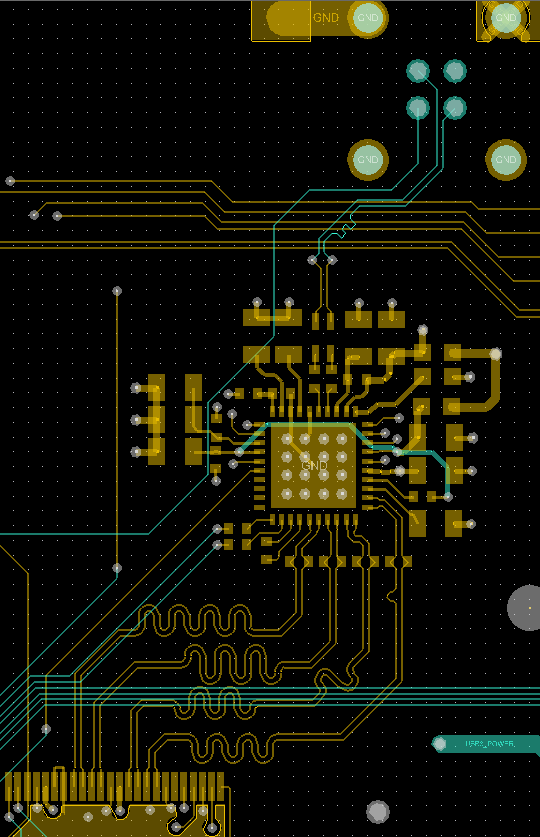

On both the ‘928q-q1 and the ‘927q-q1 the LFMODE = 0 (GND). A measurement of the differential input PCLK can be seen in the attached pictures. As example we have chosen 25MHz and 74.25MHz. With 25MHz the link is constant, with 74.25MHz there isn’t a link. The border we’ve mentioned is 42.5MHz, frequencies below were working fine, with bigger frequencies on PCLK no link becomes ready.

Question:

In addition to LFMODE=0 , which sets device to support 15MHz to 85MHz pixel clock, are there other options which must be set to operate at higher frequencies?

Thanks and regards,

Mizaur, EMEA Central Apps