Dear Specialists,

My customer is considering DS92LX1621 and DS92LX1622.

Please advise me on questions bellows related to DS92LX1622.

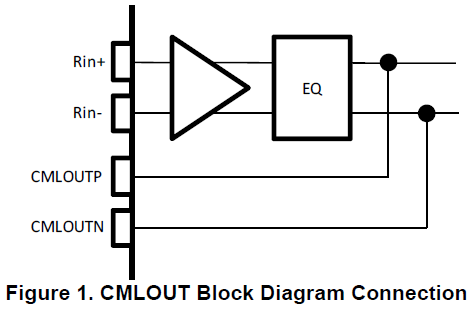

Q1. Can you let me know how to access the input signal quality on DS92LX1622 high speed input?

Q2. Referring the DS92LX1622 datasheet, the minimum input amplitude on the high speed input is

+/-90mV (180mV p-p differential) and input jitter tolerance is 0.54 UI typ.

In the meantime, the datasheet insists that the device support up to 10m STP cable transfer.

The ISI case by 10m STP may make further eye distortion.

Don’t you think there are contradict each other?

Q3. Are there any way to reflect the effect of the on chip equalizer to the eye monitoring?

Q4. One option may be provide the equalizer model to the customer and integrate such model

into a state of art oscilloscope, and compensate the monitored eye.

Is it feasible?

Q5. When you monitor the eye quality, you need information on the receiver PLL such as bandwidth

PLL type etc. Can you provide us such information?

I appreciate your great help.

Best regards,

Shinichi