Hi team,

I am looking for solution that can insert a fixed skew into a MIPI D-PHY bus.

Either between CLOCK& DATA or between P & N of the same pair.

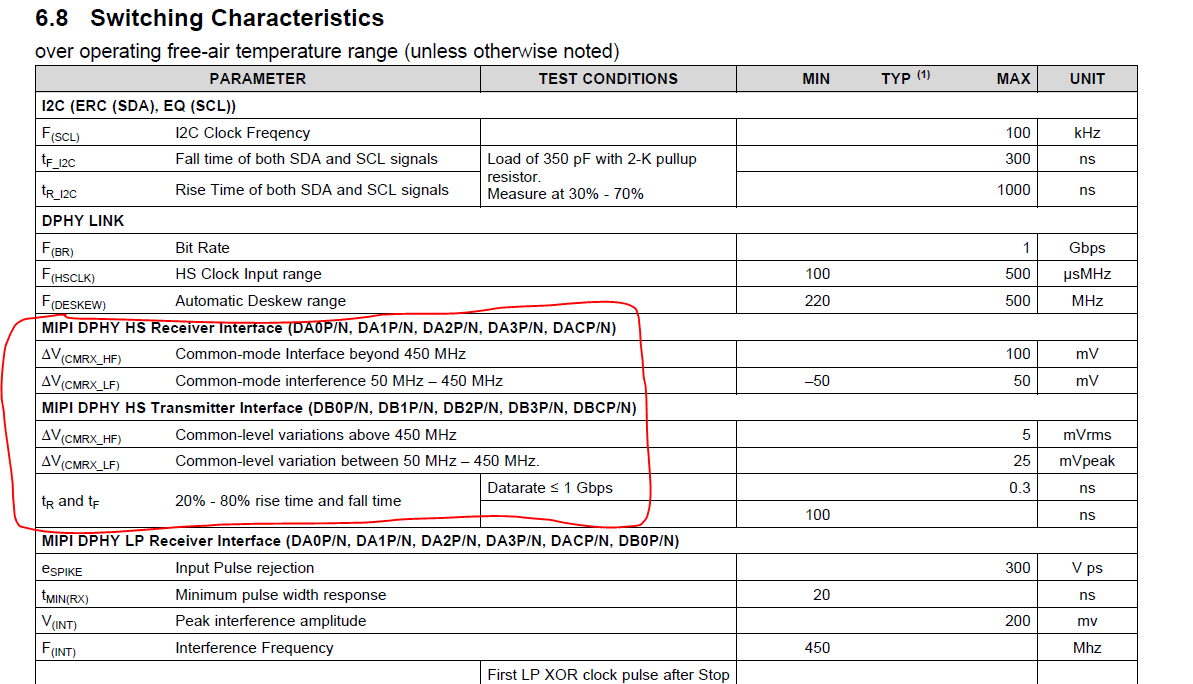

We have retiming chips available like the DPHY440. But do have similar devices that allow for fixed or configurable offset skew calibration?

Thanks, Joey