[ DS90UB940 ] [ URGENT ] Data rate and Clock Frequency

Hi,

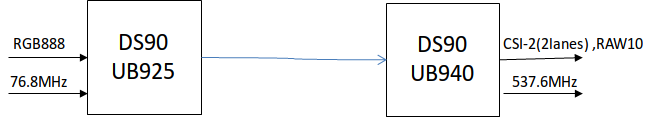

Can you help my customer to use DS90UB925 and DS90UB940 as the connection below?

What my customer expect is to have output data with 192MHz clock (76.8MHz x 2.5).

However, the clock rate is 537.6MHz and it's bigger than actual data rate.

Is there any way to have data with 192MHz?

Thank you for your support in advance.

Regards,

Ken