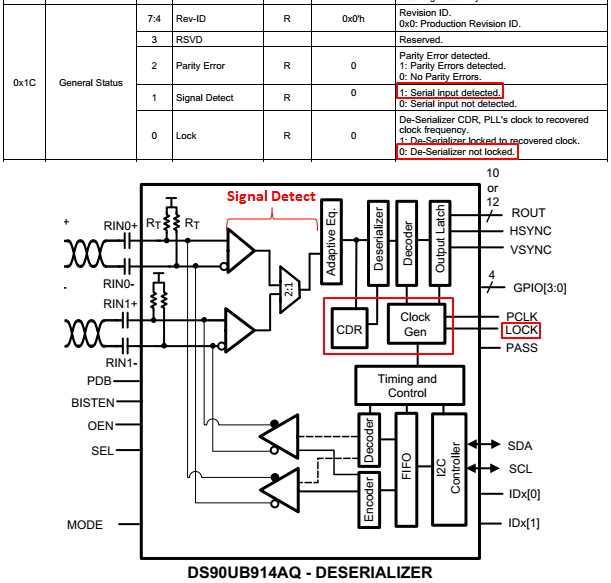

[ DS90UB914A-Q1 ] Signal Detection and LOCK Detection Circuit

Hi,

Can you please clarify the circuit or point where signal and lock are detected respectively?

At production line, customer has found that the camera image was corrupted. According to system log which DS90UB914A-Q1 is used, when this error happen, the log indicates 0x1C[0] = 0 (not locked) and 0x1C[1] = 1 (input detected). From this log, it's assumed that the out of lock condition happen, even though valid input signal appeared.

Q1: Whether the valid signal appearred or not is detected at the input stage (before signal going to CDR block).

Correct?

Q2: What situation can be expected that detect 0x1C[0] = 0 (not locked) and 0x1C[1] = 1 simultaneously?

Thanks,

Ken