Hi

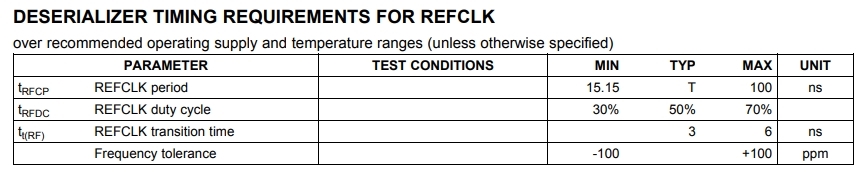

There is specification of REFCLK as the following on the datasheet.

Does this mean the RECLK should be less than TCLK +/-100ppm ?

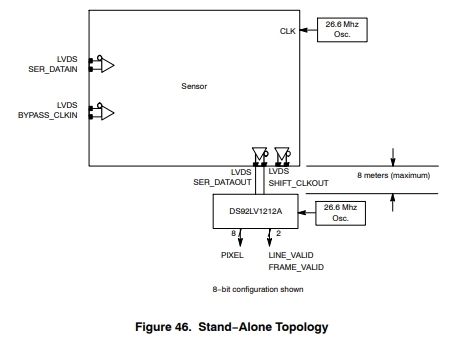

Our customer are going to replace from DS92LV1212A to SN65LV1224B because of EOL.

However it does not work as expected.(means it does not synchronize with serializer)

Could you give us any advice for this?

Best Regards,

Koji Hamamoto