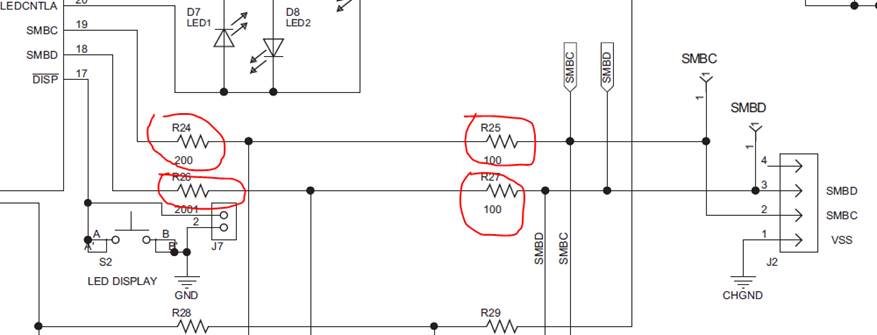

TCA9509 is used by customer with Side A as slave (batter pack, 3.3V SMBus) to Side B (MCU 5V SMBus)

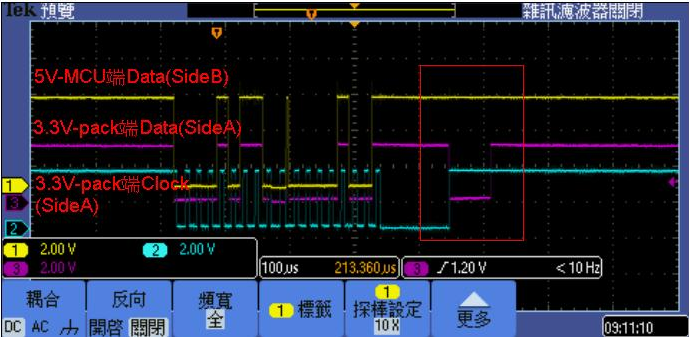

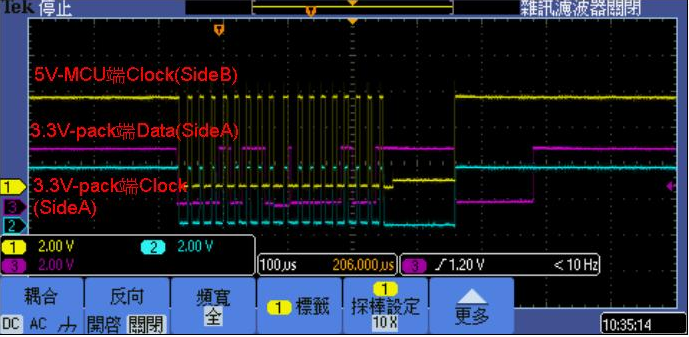

it is observed that there is ACK on side A but it is not repeated at side B

MCU data pin is set as input mode

circled in red below, Side A data purple CH has pull low

Side B data yellow CH however, didn't...what might be the cause?

the clock from side A and Side B seems normal