Other Parts Discussed in Thread: PCA9515,

Hello everybody,

Please apologize my bad english and my lack of digital skills as I'm basically an analog guy !!!

I'm having monitoring issues on an I2C bus with a PCA9515 used as a switch/buffer on the I2C entry of my daughter board (mother board I2C is not affected anyway)

If I bypass the PCA everything is working perfectly. When PCA9515A is populated, it seems that control is working (I2C Master -> slaves) but I'm having a buggy monitoring on I2C peripherals.

In it's simplest configuration, my daughter board includes only 2 I2C slaves: temp sensor MAX7500 & a demodulator STV0910 from ST.

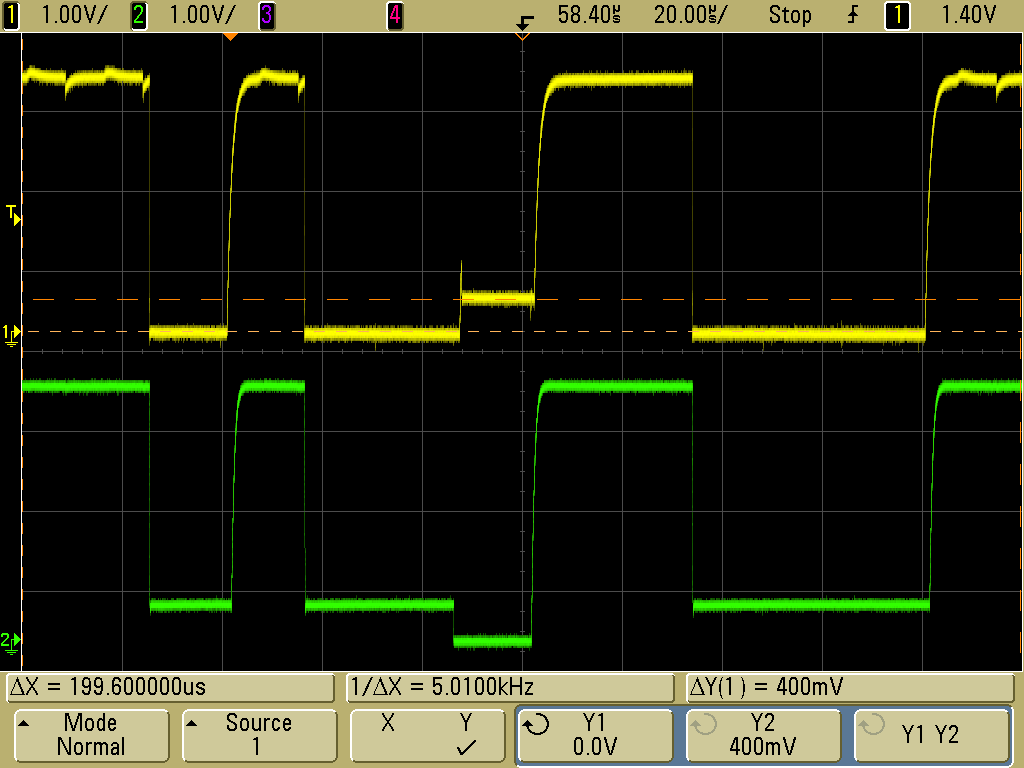

Here is an scope plot when all is OK (no PCA9515):

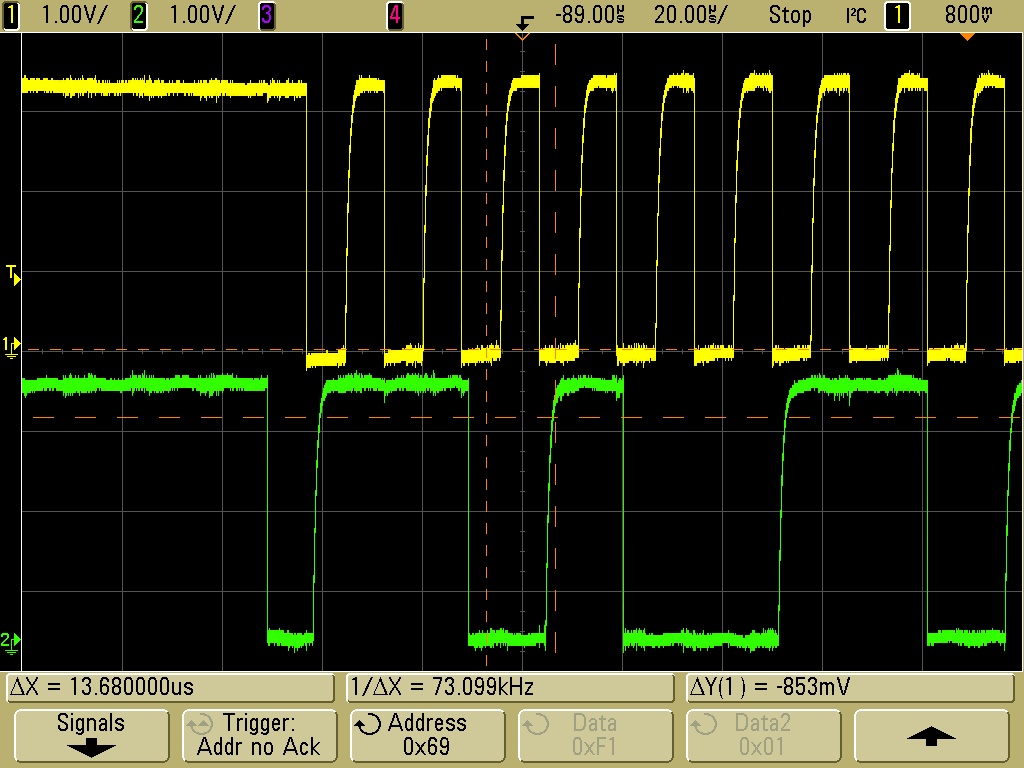

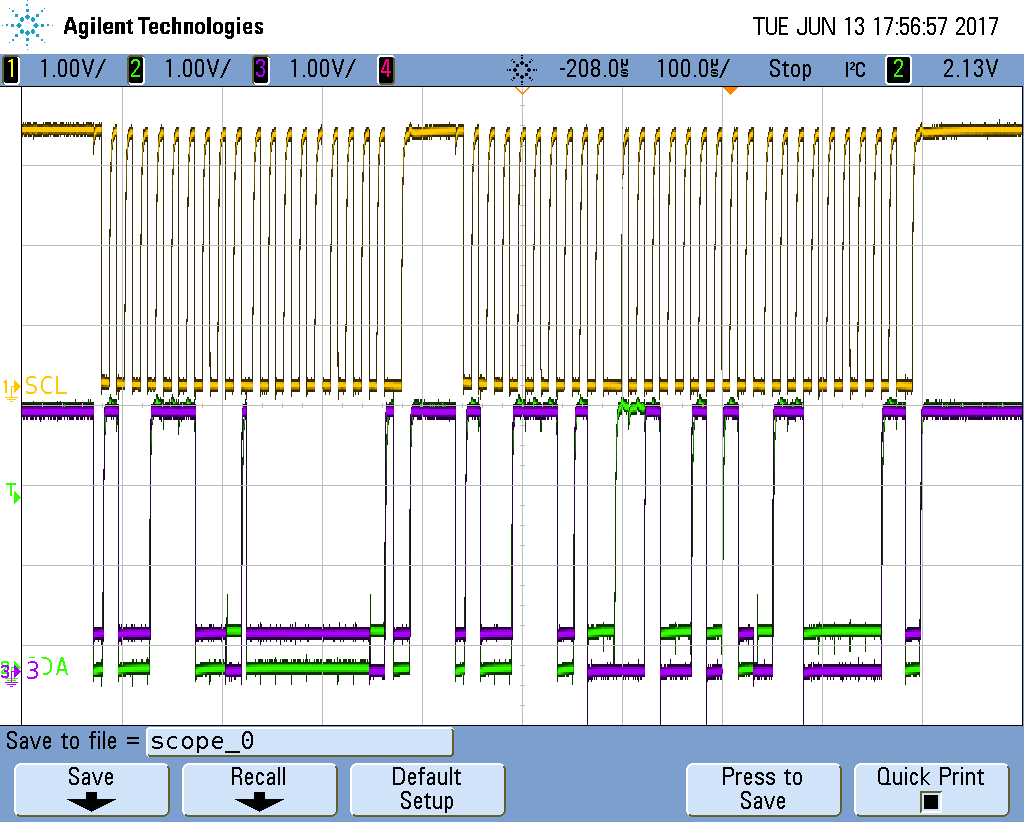

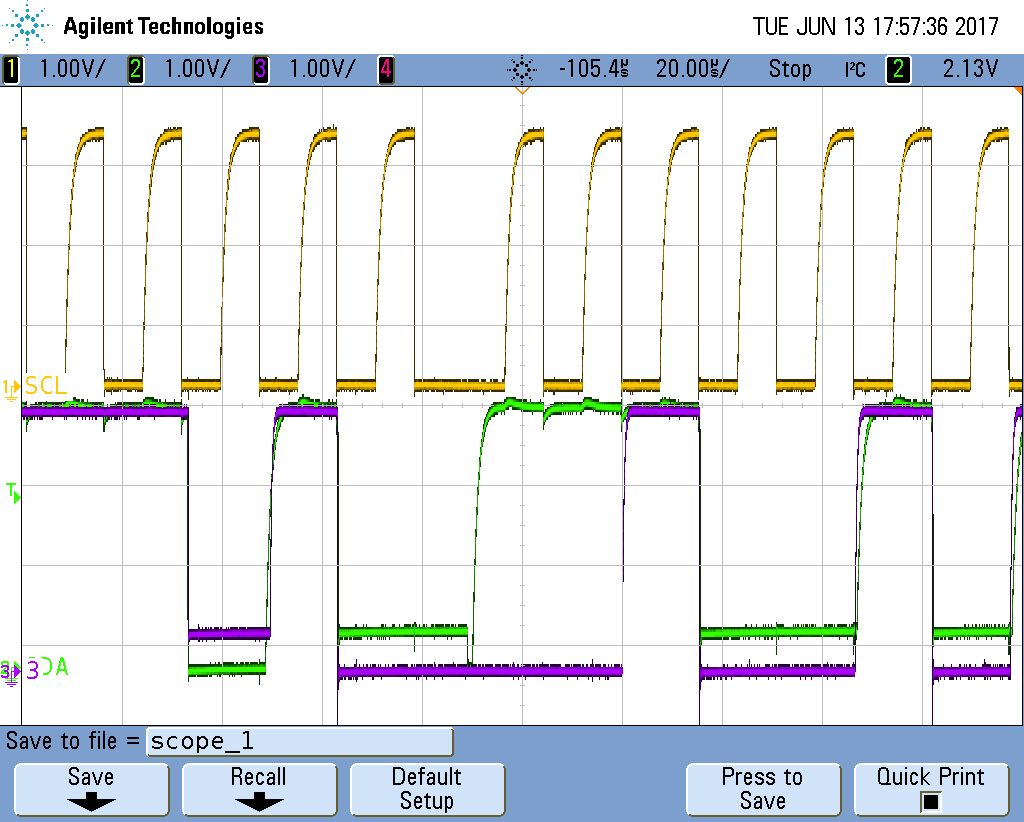

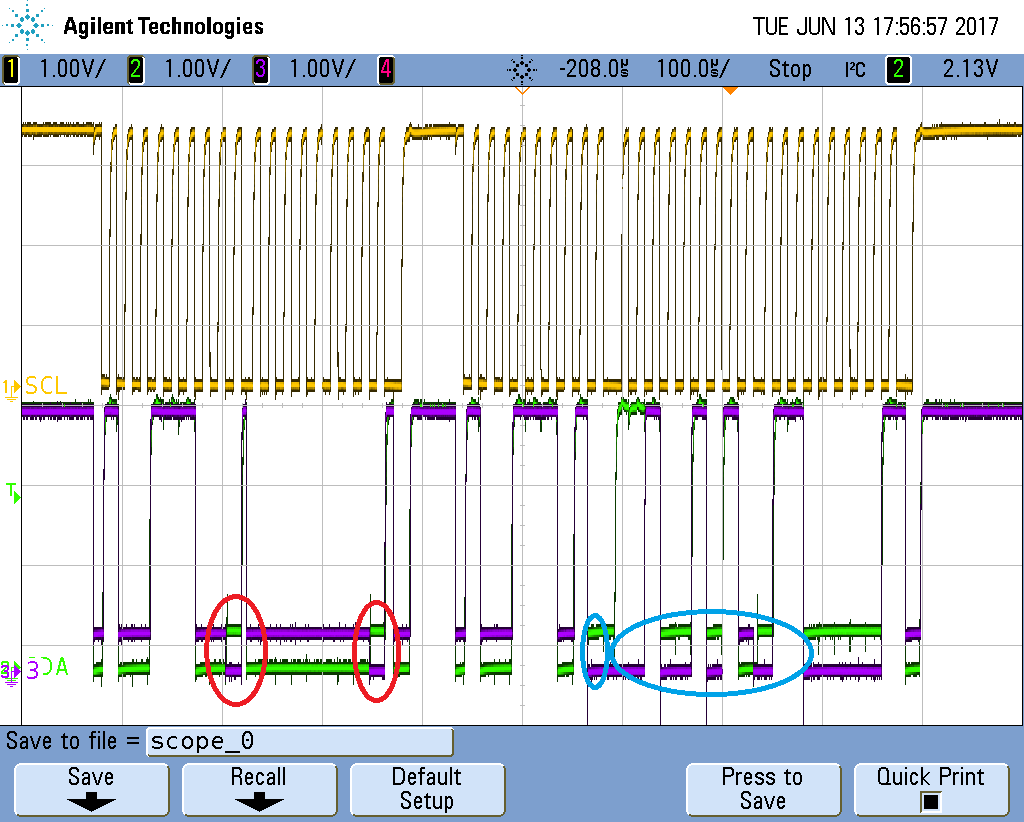

An here when PCA9515 is on the line:

I know that the 0.5V offsets are inserted by the PCA9515 to insure stability between read & write sessions on the bus but my guess is that these 0 logic level offsets could disturb the chips on the bus.

Does anybody have experienced the same troubles ?

And most important: is there a solution ?

Thank you for your help.

Yann