Other Parts Discussed in Thread: PCA9306,

Hi there supporter,

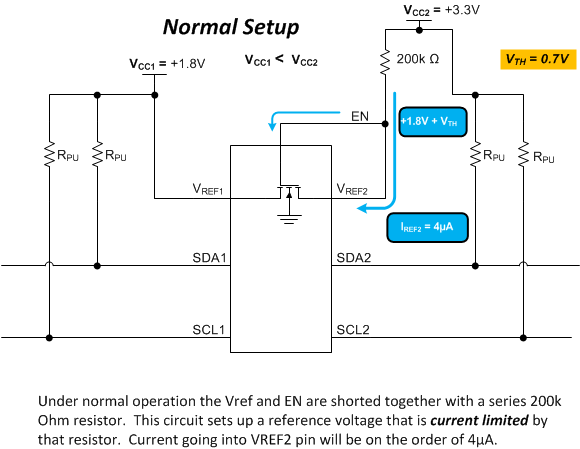

I am checking the working principle of NMOS transmission gate and I am wondering the reason why is gate bias set at approximately the VCC level of low voltage side plus one threshold voltage.

Can you let me know that?

Regards,

S.P. Lin