Hi Sirs,

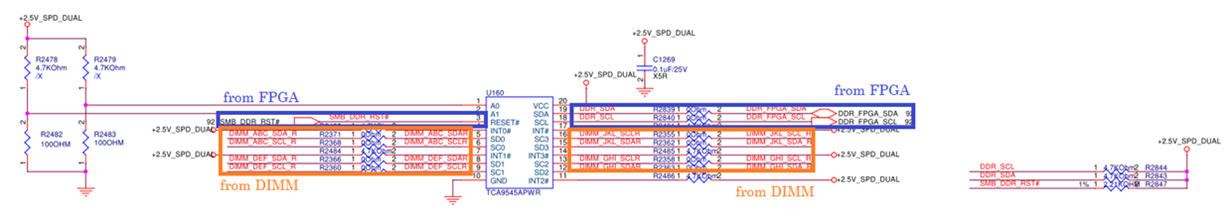

We use SMBus switch TI/ TCA9545APWR for memory in our project Oceancat.

In some of case we found BMC couldn’t read memory’s SPD information.

The TCA9545APWR power well VCC is +2.5V_SPD_DUAL and RESET is +2.5V_DUAL, the sequence is +2.5V_DUAL=>+2.5V_SPD_DUAL.

The SMBus CLK and DATA trasmited from FPGA to memory pass through the switch(TCA9545APWR).

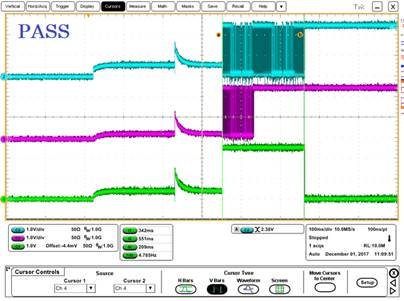

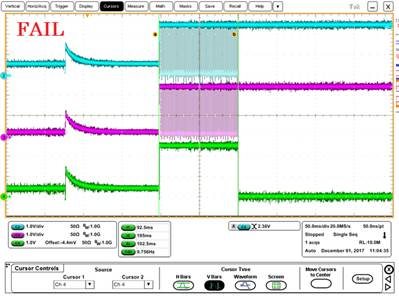

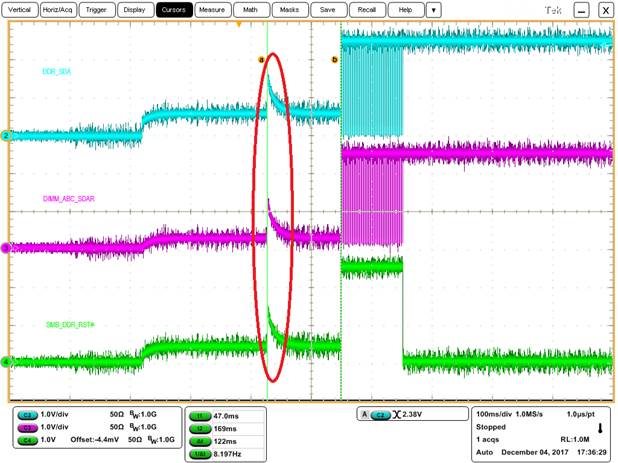

We measure waveform of the DDR_SDA, DIMM_ABC_SDAR and SMB_DDR_RST# in Pass planar and fail planar as below screenshots, please refer to it.

It show that the timing of SMB_DDR_RST# de-assert in fail planar is short than pass planar.

Please help us to check will the spike cause RST pull low earlier to result any abnormal behavior, and any sequence between VCC and RESET#

Thanks!!