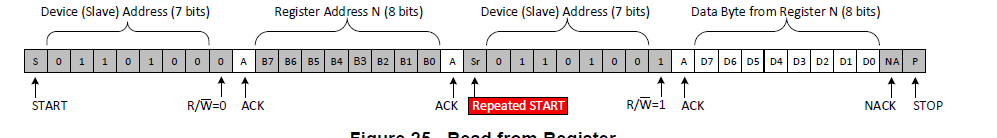

In the datasheet,8.6.2.8 GPIO Data Status Registers, GPIO_DAT_STAT1–3 (Address 0x14–0x16),there is "These registers show the GPIO state when read for inputs and outputs. Read these twice to clear them".Does that mean that I can not read the gpio state more than twice?and now I did these following in linux。

1.

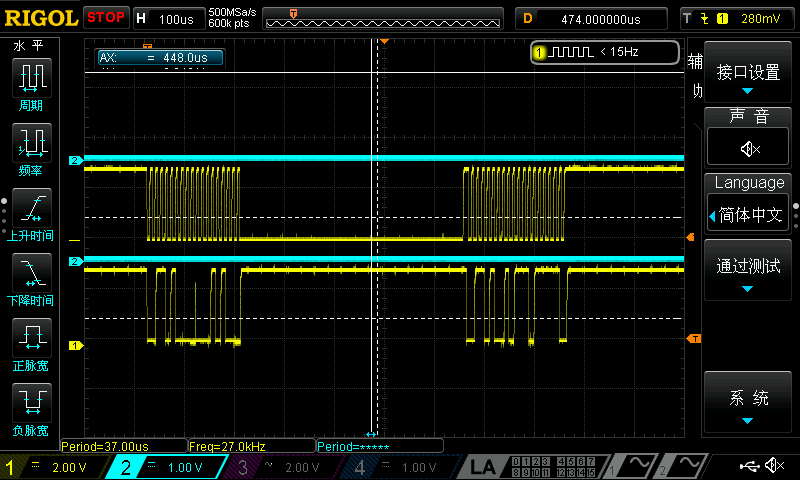

error = tca8418_write_byte(chip,REG_KP_GPIO1,0);

error = tca8418_write_byte(chip,REG_KP_GPIO2,0);

error = tca8418_write_byte(chip,REG_KP_GPIO3,0);

2.

error = tca8418_write_byte(chip,REG_GPIO_DIR1,0);

error = tca8418_write_byte(chip,REG_GPIO_DIR2,0);

error = tca8418_write_byte(chip,REG_GPIO_DIR3,0);

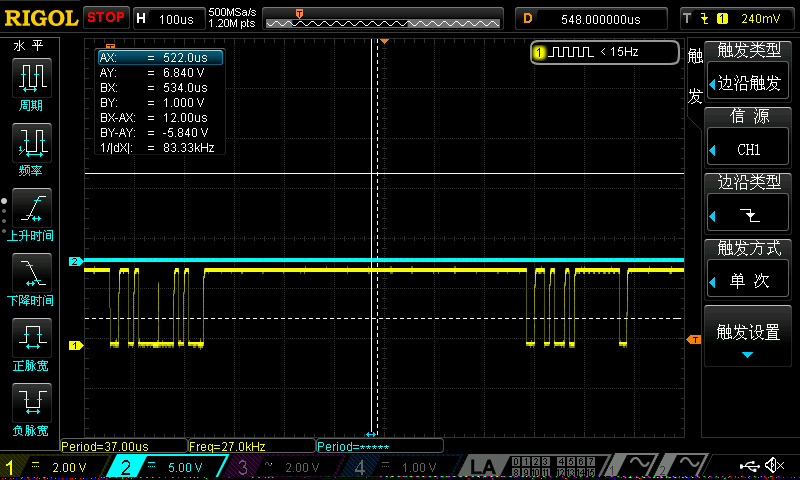

And then,when I read the reg ‘GPIO_DAT_STAT1’,I always get a constant number,like 0xbf,even if i changed the gpio level through 3.3V or GND with a 10k resistance.

so,anyone can tell me,when I want use tca8418 only in gpiomode,how should i init it, and get or set the gpio's value.