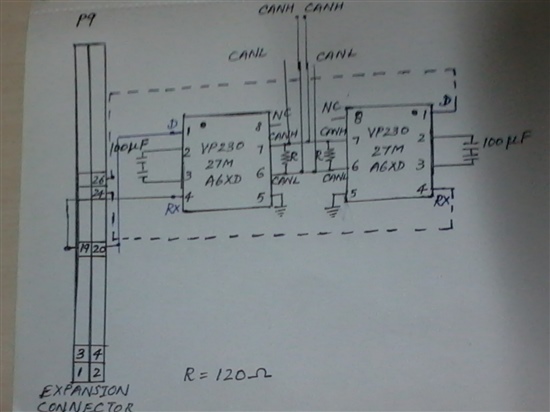

We have interfaced SN65HVD230 with Beagle Bone's CAN Port and the CAN Tx line is staying at High when we are sendingd data.We are connecting in loopback mode with one CAN transceiver CANH tied to other transceiver's CANH and similiarly for CANL also. Is there any limitation for SN65HVD230 to work with other TI's microprocessors with CAN support. The datasheeet shows operation with TMS320LF243 and is it limited to this proceesor or this is a generic transceiver ?

Please share your comments.if anybody interfaced this IC with Beagle bone and got working .