When using SN65HVD33 devices for a 4 Mbps half-duplex connection with ~4m meters of cable, 120 ohm termination at each end, we experience following behavior:

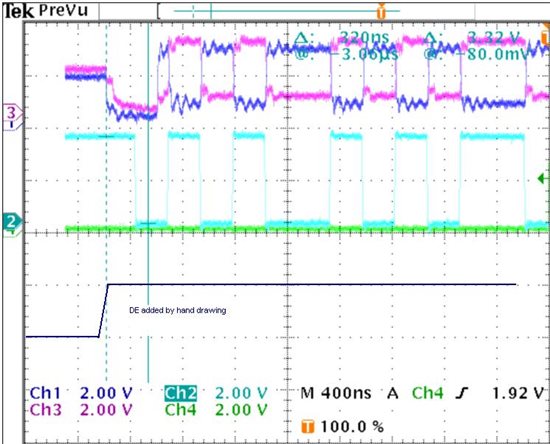

The first bit in at transmission after a bus idle is corrupted by the driver – it seems that the driver has a delay from DE=1 to Y,Z valid of ~400 ns when the bus has been idle for milliseconds. However if the idle period was less (like <100 us) DE=1 to Y,Z valid is <30 ns.

Please see below (D is channel 4, Y is channel 3, Z is channel 1, DE shifts from 0 to 1 at the dashed cursor)

A DE=1 to Y,Z valid =~ 30 ns matches to the datasheet (SLLS665I –SEPTEMBER 2005–REVISED APRIL 2010) page 6, marks 1 and 2

Whereas the ~400 ns maybe matches the mark 3 spec.

Questions:

– Is it correct that a long bus idle time (> 100 uS) will provoking a long tPZH1/tPZL1 of more than 400 ns?

1 – If yes, why and how do we avoid it?

2 – If not, what is then the cause?

- Could you please explain the spec. “Driver enable delay with bus voltage offset”