Dear,

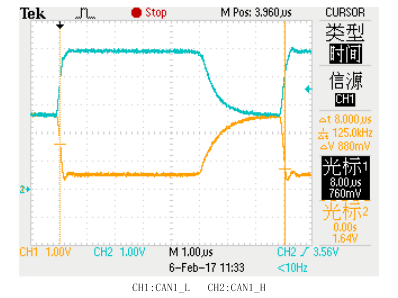

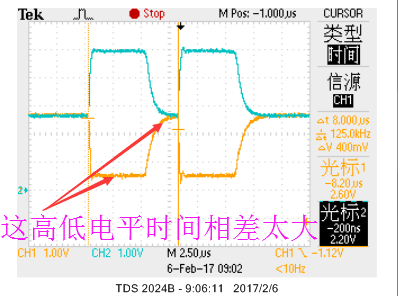

We test SN65HVD251DR and find that the time of high level is 4.6 us and the time of low level is 3.4 us. We hope that when the frequency is 250 KHz, the bit time is 4 us, and the time of high level is equal to the time of low level, the error range of bit time is 0.2% ( the average of tested 10 levels when transmitting data ). So is the next waveform normal? Could you provide the waveform of SN65HVD251DR that TI tested? How to adjust parameters to make the time of high level be equal to the time of low level?

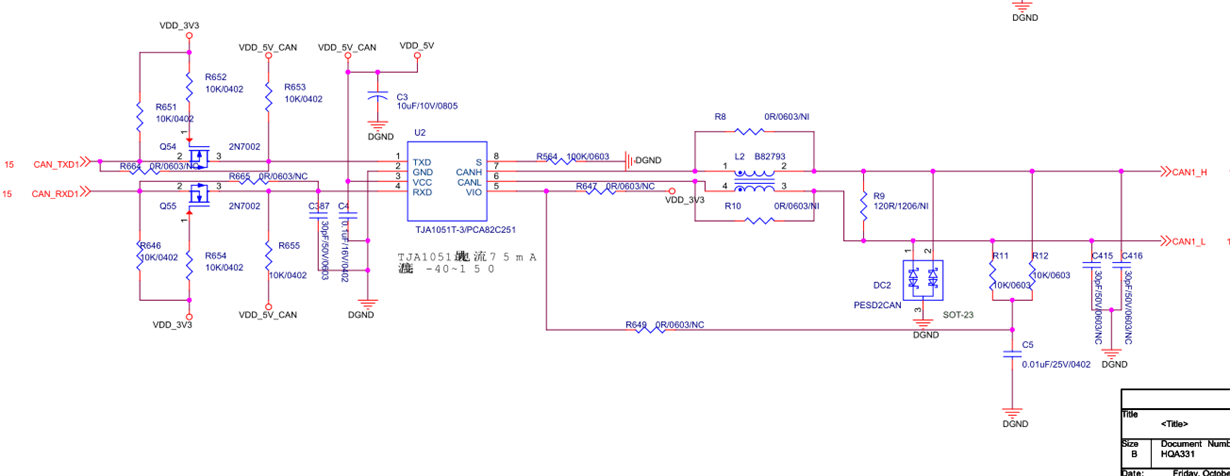

The waveform and the schematic as follows. I am waiting your reply, thank you!