Other Parts Discussed in Thread: TINA-TI

Hi, team.

My customers have started designing circuits using UCC 21520.

Although the operation is confirmed using the SPICE model of this device,

It is not an intended action.

Can you tell me whether this behavior happens even with real devices?

※ The same result will be obtained with LTspice or Tina-TI

<Question>

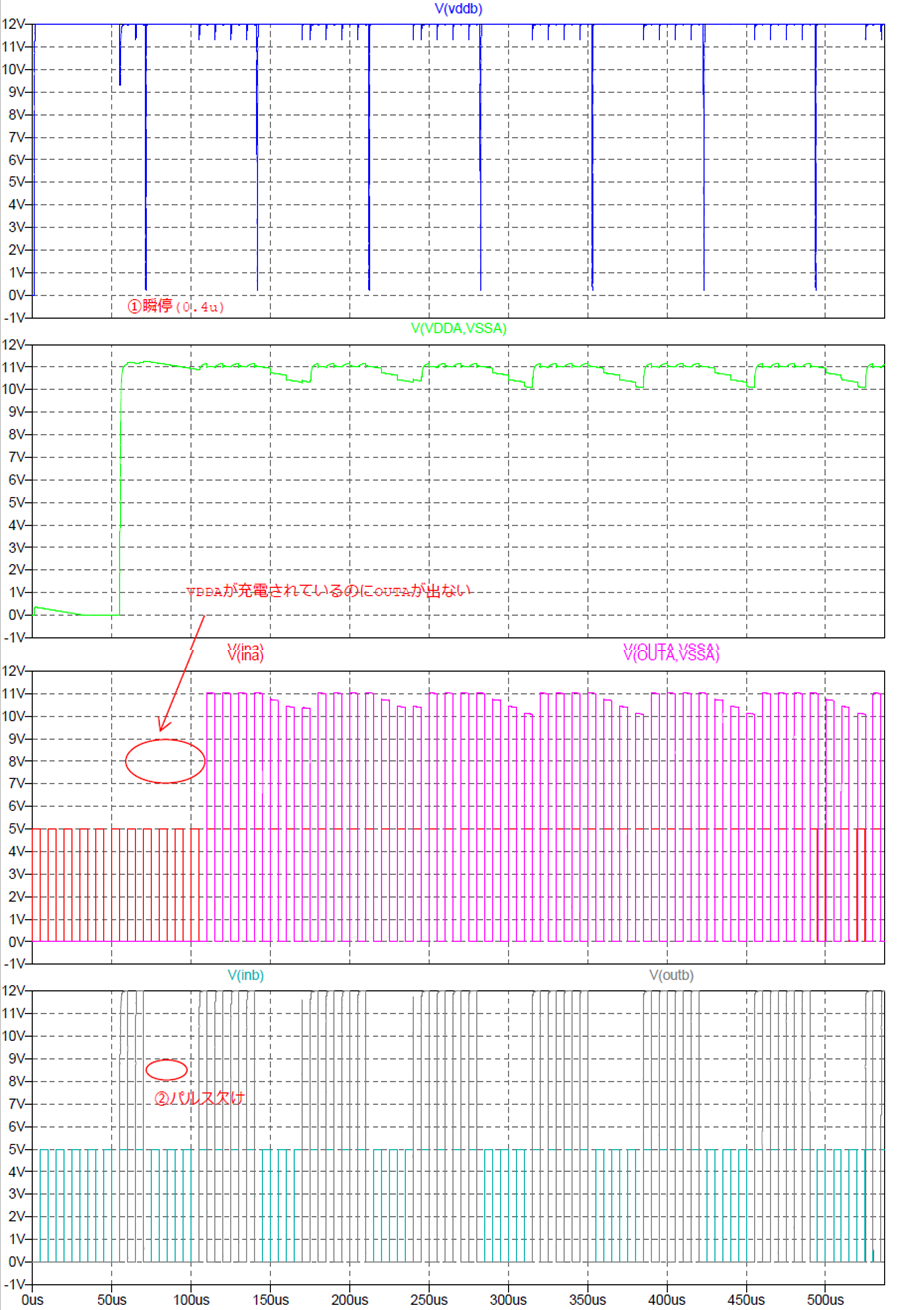

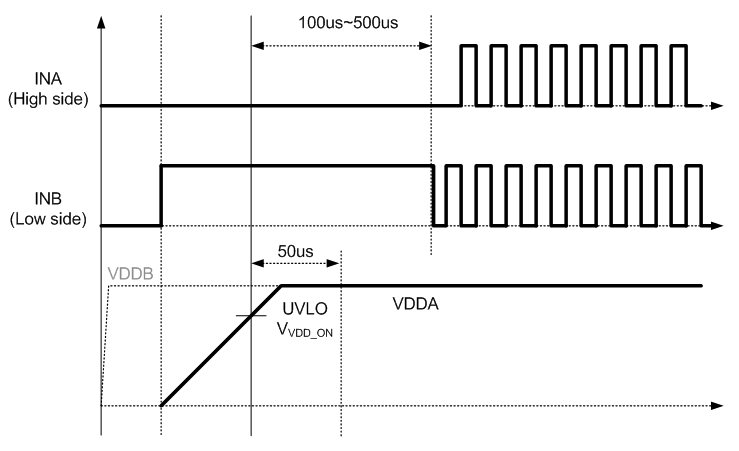

Between 30 and 60 usec after applying voltage to VDDA,

Even if a pulse is input to VINA, it is not output from VOUTA.

· Is this behavior based on the specification of UCC 21520?

· If this answer is 'yes', can you tell me the reason?

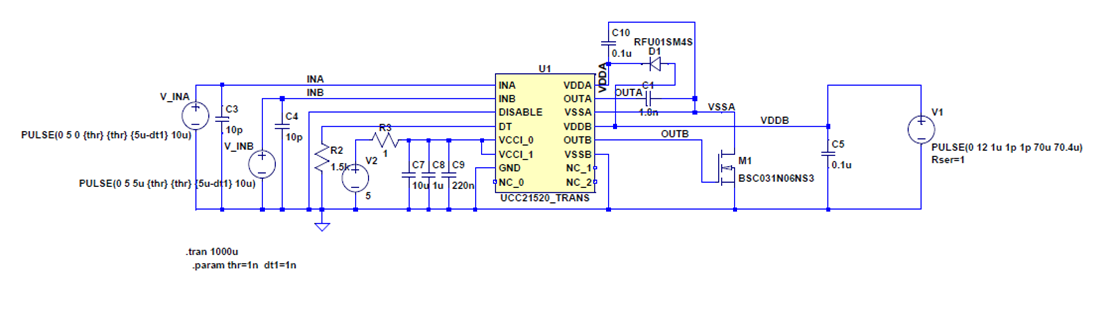

※Verification circuit diagram and waveform result are also attached

Verification Circuit

Waveform

Best regards,

Masumi Sekigcuchi