Other Parts Discussed in Thread: THVD1550, THVD1500, SN65HVD3088E, SN65HVD82

To whom it may concern,

We are using the SN65176B chip in a J1708 application as described in 'J1708 Bus Loading' section of the following TI app note:

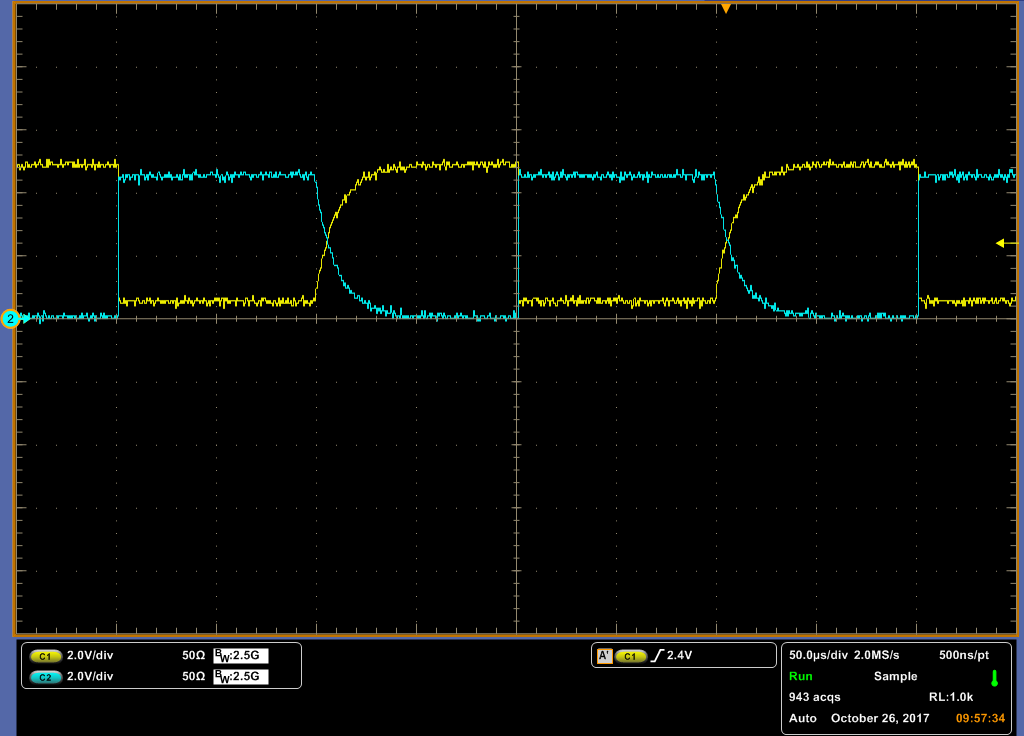

When measuring the signals I noticed that there is an imbalance between Port A/B outputs when disabling the driver and relying on the termination described in this app note. The termination is symmetrical, yet the Port A rises faster than the Port B falls when the driver is disabled.

I noticed from the datasheet that there is an imbalance in these outputs in the tPHZ and tPLZ delays, with maximums stated as 250ns and 30ns (respectively). Based on this I have the following questions:

- Does this imbalanced delay also have something to do with the edge speed imbalance I am seeing, even though the termination on the outputs is symmetrical?

-> If so, what specifically is the cause and do we need to compensate this externally by decreasing the value of the pull-down on Port B w.r.t the pull-up on Port A?

-> If this is the case, could you suggest something that still meets the AM/FM interference rejection requirements of the J1708 specification?

Look forward to your response.

Many Thanks,

Bhav