Other Parts Discussed in Thread: TLK10022

We are going to use the TLK1002 to perform the serialization / deserialization of the TMDS lines of an HDMI / DVI signal, but have a few questions :

1. The Clocking examples of the TLK10022 datasheet shows the high-speed-line-side rate as 4 times (4:1) ,3 times (3:1) or 2 times (2:1) the low-speed-line-side rate.

If the 8b/10b encoder is used, Should the high-speed-line-side be multiplied per the 10/8 factor?

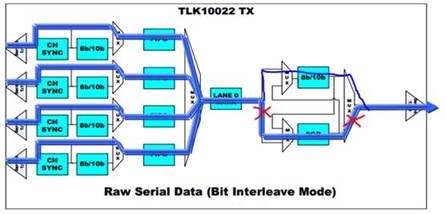

Is the bit interleaving mode and 8b/10b encoding supported?

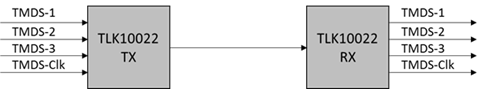

2. My application is the DVI interface TMDS signals aggregation / de-aggregation. Since the TMDS consists in 3 data signals (RGB components) and their synchronous pixel-clock , it would not be exactly the aggregation of serial-lanes but I think it could be achieved in this two ways:

a) To use the TLK10022 in 4:1 bit interleave mode and to insert the pixel-clock signal as the fourth lane:

The TMDS-clock frequency will be 1/10 of TMDS signals data rate, so it could be treated as a 1/5 data rate signal. ¿Could the TMDS-Clk be oversampled on the TLK10022-Tx device and then restored in the TLK10022-Rx device?

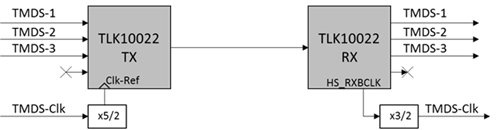

b) To use the TLK10022 in 3:1 mode, force the pixel-clock to be the reference of the high-speed-line-side clock and to generate again the pixel-clock from the RX recovered clock:

ie: Resolution XGA(1024x768@60Hz) => TMDS_signals data rate = 0,65Gbps, TMDS_Clock = 65MHz.

Low-speed SERDES (0,65Gbps) should work at quarter rate and High-speed SERDES (1,95Gbps) should work at quarter rate too. Low speed PLL multiplier could be 8x and High-speed PLL 12x.

So, the Reference_clock needed will be (0,65Gbps x 2/8) = (TMDS_Clock x 5/2).

On RX we could use HS_RXBCLK = High_speed_data_rate /20 and generate again the TMDS_clock = HS_RXBCLK x3/2.

Would the TLK100022 work properly in this application? Could you provide any advice?

Thanks in advance

Gabriel Cutillas