Dear Sir/Madam,

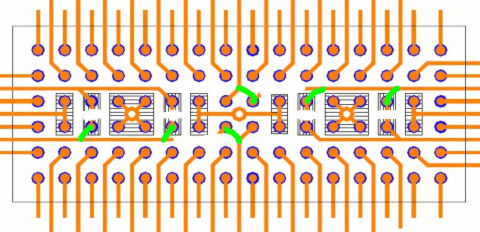

In SN74AVC32T245 datasheet figure 14, provided layout diagram will only match for 32 buffer/driver routing. Since it uses only single supply. Kindly provide layout diagram for voltage level translator where two supply are used VCCA and VCCB.